Through-silicon via

In electronic engineering, a through-silicon via (TSV) is a vertical electrical connection (via) passing completely through a silicon wafer or die. TSVs are a high performance interconnect techniques used as an alternative to wire-bond and flip chips to create 3D packages and 3D integrated circuits, compared to alternatives such as package-on-package, because the density of the vias is substantially higher, and because the length of the connections is shorter.

Using TSVs it is possible to achieve connections through the front end of line (FEOL).

Image sensors

CMOS image sensors (CIS) were among the first applications to adopt TSV(s) in volume manufacturing. In initial CIS applications, TSVs were formed on the backside of the image sensor wafer to form interconnects, eliminate wire bonds, and allow for reduced form factor and higher-density interconnects. Chip stacking only came about with the advent of backside illuminated (BSI) CIS, and involved reversing the order of the lens, circuitry, and photodiode from traditional front-side illumination so that the light coming through the lens first hits the photodiode and then the circuitry. This was accomplished by flipping the photodiode wafer, thinning the backside, and then bonding it on top of the readout layer using a direct oxide bond, with TSVs as interconnects around the perimeter.[1]

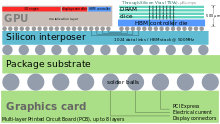

3D packages

A 3D package (System in Package, Chip Stack MCM, etc.) contains two or more chips (integrated circuits) stacked vertically so that they occupy less space and/or have greater connectivity. An alternate type of 3D package can be found in IBM's Silicon Carrier Packaging Technology, where ICs are not stacked but a carrier substrate containing TSVs is used to connect multiple ICs together in a package. In most 3D packages, the stacked chips are wired together along their edges; this edge wiring slightly increases the length and width of the package and usually requires an extra “interposer” layer between the chips. In some new 3D packages, TSVs replace edge wiring by creating vertical connections through the body of the chips. The resulting package has no added length or width. Because no interposer is required, a TSV 3D package can also be flatter than an edge-wired 3D package. This TSV technique is sometimes also referred to as TSS (Through-Silicon Stacking or Thru-Silicon Stacking).

3D integrated circuits

A 3D integrated circuit (3D IC) is a single integrated circuit built by stacking silicon wafers and/or dies and interconnecting them vertically so that they behave as a single device. By using TSV technology, 3D ICs can pack a great deal of functionality into a small “footprint.” The different devices in the stack may be heterogeneous, e.g. combining CMOS logic, DRAM and III-V materials into a single IC. In addition, critical electrical paths through the device can be drastically shortened, leading to faster operation. The Wide I/O 3D DRAM memory standard (JEDEC JESD229) includes TSV in the design.[2]

History of the term

The first TSV was patented by William Shockley in 1962,[3] although most people in the electronics industry consider Merlin Smith and Emanuel Stern of IBM the inventors of TSV, based on their patent “Methods of Making Thru-Connections in Semiconductor Wafers” filed on December 28, 1964 and granted on September 26, 1967.

However, it wasn't until the late 1990s that the term "Through Silicon Via" was coined by Dr. Sergey Savastiouk, the co-founder and current CEO of ALLVIA Inc.as part of his original business plan. From the beginning, the vision of the business plan was to create a through silicon interconnect since these would offer significant performance improvements over wire bonds. Savastiouk published two articles on the topic in Solid State Technology, first in January 2000 and again in 2010. The first article “Moore’s Law – The Z Dimension” was published in Solid State Technology magazine in January 2000.[4] This article outlined the roadmap of the TSV development as a transition from 2D chip stacking to wafer level stacking in the future. In one of the sections titled Through Silicon Vias, Dr. Sergey Savastiouk wrote, “Investment in technologies that provide both wafer-level vertical miniaturization (wafer thinning) and preparation for vertical integration (through silicon vias) makes good sense.” He continued, “By removing the arbitrary 2D conceptual barrier associated with Moore’s Law, we can open up a new dimension in ease of design, test, and manufacturing of IC packages. When we need it the most – for portable computing, memory cards, smart cards, cellular phones, and other uses – we can follow Moore’s Law into the Z dimension.” This was the first time the term "through-silicon via" was used in a technical publication.

References

- ↑ F. von Trapp, The Future Of Image Sensors is Chip Stacking http://www.3dincites.com/2014/09/future-image-sensors-chip-stacking

- ↑ Desjardins, Emily. "JEDEC Publishes Breakthrough Standard for Wide I/O Mobile DRAM". JEDEC. JEDEC. Retrieved 1 December 2014.

- ↑ J.H. Lau, Who Invented the Through Silicon Via (TSV) and When? 3D InCites, 2010, http://www.3dincites.com/2010/04/who-invented-the-through-silicon-via-tsv-and-when/

- ↑ AUTHOR(S)Savastiouk, Sergey, Moore's Law in the Z-Direction, Solid State Technology; Jan 2000, Vol. 43 Issue 1, p84 http://connection.ebscohost.com/c/articles/2668333/moores-law-z-dimension

- http://realworldtech.com/page.cfm?ArticleID=RWT050207213241

- http://www.appliedmaterials.com/technologies/library/producer-avila-pecvd

- http://www.businesswire.com/portal/site/appliedmaterials/permalink/?dmViewId=news_view&newsId=20100712005576&newsLang=en

- http://www.google.com/patents/US7683459

- http://www.google.com/patents/US7633165

- http://www.icemostech.com/ice/