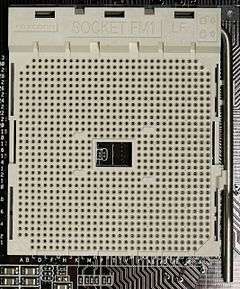

Socket FM1

| |

| Type | PGA-ZIF |

|---|---|

| Chip form factors | PGA |

| Contacts | 905 |

| FSB protocol | Unified Media Interface (UMI) |

| FSB frequency |

100 MHz System clock Unified Media Interface up to 5,2 GT/s |

| Processors | early A-series APUs |

| Successor | FM2 |

|

This article is part of the CPU socket series | |

Socket FM1 is a CPU socket for desktop computers used by AMD early A-series APUs ("Llano") processors and Llano-derived Athlon II processors. It was released in July 2011. Its direct successors are Socket FM2 (September 2012) and Socket FM2+ (January 2014), while Socket AM1 (January 2014) is targeting low-power SoCs.

For available chipsets consult Fusion controller hubs (FCH).

Feature overview for AMD APUs

| Brand | Llano | Trinity | Richland | Kaveri | Carrizo | Bristol Ridge | Raven Ridge | Desna, Ontario, Zacate | Kabini, Temash | Beema, Mullins | Carrizo-L | Stoney Ridge | |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Platform | Desktop, Mobile | Mobile | Desktop, Mobile | Ultra-mobile | |||||||||

| Released | Aug 2011 | Oct 2012 | Jun 2013 | Jan 2014 | Jun 2015 | Jun 2016 | May 2017 | Jan 2011 | May 2013 | Q2 2014 | May 2015 | June 2016 | |

| Fab. (nm) | GlobalFoundries 32 SOI | 28 | 14 | TSMC 40 | 28 | ||||||||

| Die size (mm2) | 228 | 246 | 245 | 244.62 | 250.04 | TBA | 75 (+ 28 FCH) | ~107 | TBA | 125 | |||

| Socket | FM1, FS1 | FM2, FS1+, FP2 | FM2+, FP3 | FM2+, FP4 | FP4 | AM4, FP5 | FT1 | AM1, FT3 | FT3b | FP4 | FP4 | ||

| CPU architecture | AMD 10h | Piledriver | Steamroller | Excavator | Zen | Bobcat | Jaguar | Puma | Puma+[1] | Excavator | |||

| Memory support | DDR3-1866 DDR3-1600 DDR3-1333 | DDR3-2133 DDR3-1866 DDR3-1600 DDR3-1333 | DDR4-2400 DDR4-2133 DDR4-1866 DDR4-1600 | DDR3L-1333 DDR3L-1066 | DDR3L-1866 DDR3L-1600 DDR3L-1333 DDR3L-1066 | DDR3L-1866 DDR3L-1600 DDR3L-1333 | Up to DDR4-2133 | ||||||

| 3D engine[lower-alpha 1] | TeraScale (VLIW5) | TeraScale (VLIW4) | GCN 2nd Gen (Mantle, HSA) | GCN 3rd Gen (Mantle, HSA) | GCN 4th Gen[2] (Mantle, HSA) | TeraScale (VLIW5) | GCN 2nd Gen | GCN 3rd Gen[3] | |||||

| Up to 400:20:8 | Up to 384:24:6 | Up to 512:32:8 | Up to 768:48:12 | 80:8:4 | 128:8:4 | Up to 192:?:? | |||||||

| IOMMUv1 | IOMMUv2 | IOMMUv1[4] | TBA | TBA | |||||||||

| Unified Video Decoder | UVD 3 | UVD 4.2 | UVD 6 | TBA | UVD 3 | UVD 4 | UVD 4.2 | UVD 6 | UVD 6.3 | ||||

| Video Coding Engine | N/A | VCE 1.0 | VCE 2.0 | VCE 3.1 | TBA | N/A | VCE 2.0 | VCE 3.1 | |||||

| GPU power saving | PowerPlay | PowerTune | N/A | PowerTune[5] | |||||||||

| Max. displays[lower-alpha 2] | 2–3 | 2–4 | 2–4 | 3 | 4 | TBA | 2 | TBA | TBA | ||||

| TrueAudio | N/A | ✔[7] | N/A[4] | TBA | |||||||||

| FreeSync | N/A | ✔ | N/A | TBA | |||||||||

/drm/radeon[8][9] |

✔ | N/A | ✔ | N/A | |||||||||

/drm/amd/amdgpu[10] |

N/A | ✔[11] | ✔ | N/A | ✔[11] | ✔ | |||||||

- ↑ Unified shaders : texture mapping units : render output units

- ↑ To feed more than two displays, the additional panels must have native DisplayPort support.[6] Alternatively active DisplayPort-to-DVI/HDMI/VGA adapters can be employed.

See also

References

- ↑ "AMD Mobile "Carrizo" Family of APUs Designed to Deliver Significant Leap in Performance, Energy Efficiency in 2015" (Press release). 2014-11-20. Retrieved 2015-02-16.

- ↑ "AMD VEGA10 and VEGA11 GPUs spotted in OpenCL driver". VideoCardz.com. Retrieved 3 September 2016.

- ↑ "AMD VEGA10 and VEGA11 GPUs spotted in OpenCL driver". VideoCardz.com. Retrieved 3 September 2016.

- 1 2 Thomas De Maesschalck (2013-11-14). "AMD teases Mullins and Beema tablet/convertibles APU". Retrieved 2015-02-24.

- ↑ Tony Chen; Jason Greaves, "AMD's Graphics Core Next (GCN) Architecture" (PDF), AMD, retrieved 2016-08-13

- ↑ "How do I connect three or More Monitors to an AMD Radeon™ HD 5000, HD 6000, and HD 7000 Series Graphics Card?". AMD. Retrieved 2014-12-08.

- ↑ "A technical look at AMD's Kaveri architecture". Semi Accurate. Retrieved 6 July 2014.

- ↑ Airlie, David (2009-11-26). "DisplayPort supported by KMS driver mainlined into Linux kernel 2.6.33". Retrieved 2016-01-16.

- ↑ "Radeon feature matrix". freedesktop.org. Retrieved 2016-01-10.

- ↑ Deucher, Alexander (2015-09-16). "XDC2015: AMDGPU" (PDF). Retrieved 2016-01-16.

- 1 2 Michel Dänzer (2016-11-17). "[ANNOUNCE] xf86-video-amdgpu 1.2.0". lists.x.org.

- http://www.tomshardware.com/news/amd-llano-socket-fm1-sample,12549.html

- http://www.amd.com/us/products/desktop/processors/a-series/Pages/a-series-model-number-comparison.aspx

This article is issued from Wikipedia - version of the 8/18/2016. The text is available under the Creative Commons Attribution/Share Alike but additional terms may apply for the media files.