# **RF** Microelectronics

Second Edition

**Behzad Razavi**

Prentice Hall Communications Engineering and Emerging Technologies Series

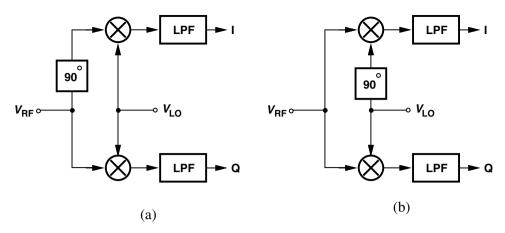

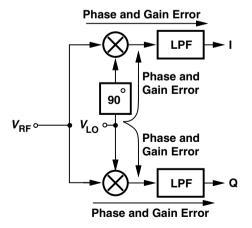

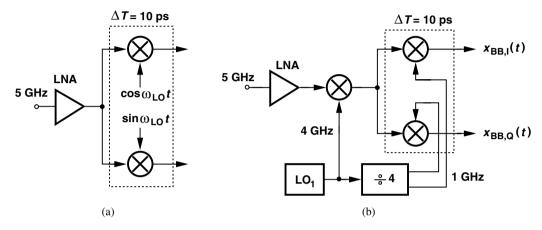

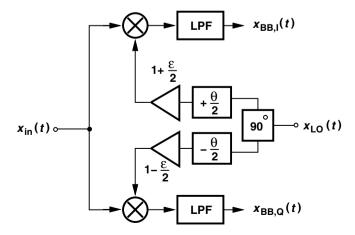

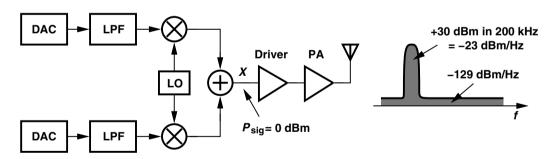

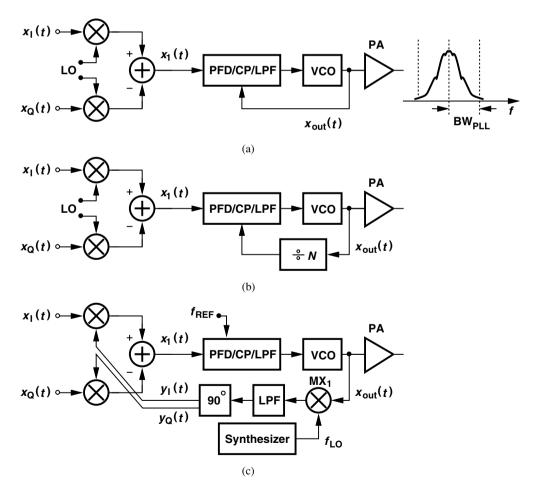

Theodore S. Rappaport, Series Editor

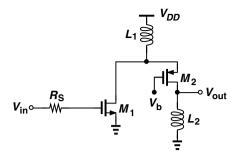

# **RF MICROELECTRONICS**

**Second Edition**

# RF MICROELECTRONICS

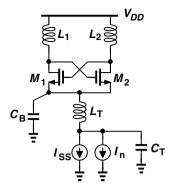

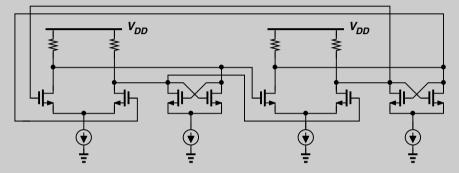

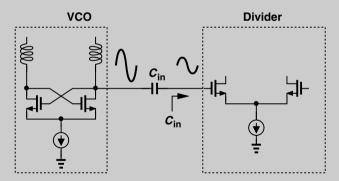

**Second Edition**

Behzad Razavi

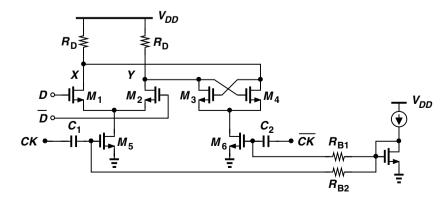

Many of the designations used by manufacturers and sellers to distinguish their products are claimed as trademarks. Where those designations appear in this book, and the publisher was aware of a trademark claim, the designations have been printed with initial capital letters or in all capitals.

The author and publisher have taken care in the preparation of this book, but make no expressed or implied warranty of any kind and assume no responsibility for errors or omissions. No liability is assumed for incidental or consequential damages in connection with or arising out of the use of the information or programs contained herein.

The publisher offers excellent discounts on this book when ordered in quantity for bulk purchases or special sales, which may include electronic versions and/or custom covers and content particular to your business, training goals, marketing focus, and branding interests. For more information, please contact:

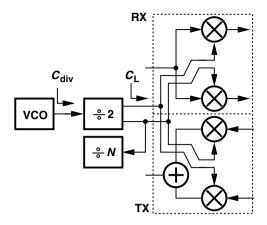

U.S. Corporate and Government Sales (800) 382-3419 corpsales@pearsontechgroup.com

For sales outside the United States, please contact:

International Sales international@pearson.com

Visit us on the Web: informit.com/ph

Library of Congress Cataloging-in-Publication Data

Razavi, Behzad.

RF microelectronics / Behzad Razavi.—2nd ed.

p. cm.

Includes bibliographical references and index.

ISBN 978-0-13-713473-1 (hardcover : alk. paper) 1. Radio frequency integrated circuits—Design and construction. I. Title.

TK6560.R39 2011 621.384'12—dc23

2011026820

Copyright © 2012 Pearson Education, Inc.

All rights reserved. Printed in the United States of America. This publication is protected by copyright, and permission must be obtained from the publisher prior to any prohibited reproduction, storage in a retrieval system, or transmission in any form or by any means, electronic, mechanical, photocopying, recording, or likewise. To obtain permission to use material from this work, please submit a written request to Pearson Education, Inc., Permissions Department, One Lake Street, Upper Saddle River, New Jersey 07458, or you may fax your request to (201) 236-3290.

ISBN-13: 978-0-13-713473-1 ISBN-10: 0-13-713473-8

Text printed in the United States at Hamilton Printing Company in Castleton, New York. First printing, September 2011

**Publisher** Paul Boger

Acquisitions Editor Bernard Goodwin

Managing Editor John Fuller

Full-Service Production Manager Julie B. Nahil

Copy Editor

Geneil Breeze

Indexer Ted Laux

Proofreader Linda Seifert

**Publishing Coordinator** Michelle Housley

Cover Designer Gary Adair

Compositor LaurelTech

# **CONTENTS**

| PREFACE TO THE SECOND EDITION |        |                                 | XV    |

|-------------------------------|--------|---------------------------------|-------|

| PREFACE TO THE FIRST EDITION  |        |                                 | xix   |

| ACKNOWLEDGMENTS               |        |                                 | xxi   |

| ABOUT T                       | THE AU | THOR                            | xxiii |

|                               |        |                                 |       |

| <b>CHAPTI</b>                 | ER 1   | INTRODUCTION TO RF AND WIRELESS |       |

|                               |        | TECHNOLOGY                      | 1     |

| 1.1                           | A Wi   | reless World                    | 1     |

| 1.2                           | RF D   | esign Is Challenging            | 3     |

| 1.3                           | The E  | Big Picture                     | 4     |

| Refe                          | rences |                                 | 5     |

| CHAPTI                        | ER 2   | BASIC CONCEPTS IN RF DESIGN     | 7     |

| 2.1                           |        | ral Considerations              | 7     |

|                               | 2.1.1  | Units in RF Design              | 7     |

|                               | 2.1.2  | Time Variance                   | 9     |

|                               | 2.1.3  | Nonlinearity                    | 12    |

| 2.2                           |        | ts of Nonlinearity              | 14    |

|                               | 2.2.1  | •                               | 14    |

|                               | 2.2.2  | Gain Compression                | 16    |

|                               | 2.2.3  | Cross Modulation                | 20    |

|                               | 2.2.4  | Intermodulation                 | 21    |

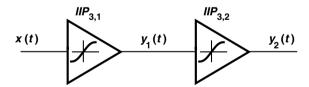

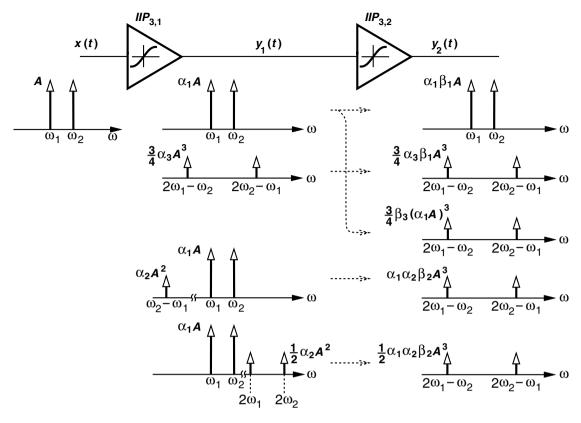

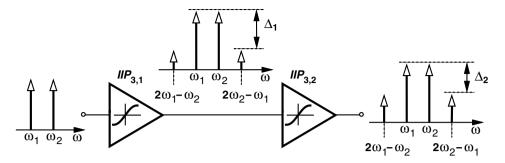

|                               | 2.2.5  | Cascaded Nonlinear Stages       | 29    |

|                               | 2.2.6  | AM/PM Conversion                | 33    |

| 2.3                           | Noise  | ,                               | 35    |

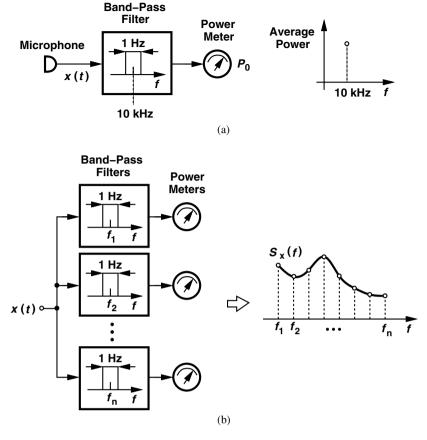

|                               | 2.3.1  | Noise as a Random Process       | 36    |

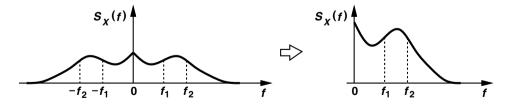

|                               | 2.3.2  | Noise Spectrum                  | 37    |

viii Contents

|       | 2.3.3   | Effect of Transfer Function on Noise       | 39  |

|-------|---------|--------------------------------------------|-----|

|       | 2.3.4   | Device Noise                               | 40  |

|       | 2.3.5   | Representation of Noise in Circuits        | 46  |

| 2.4   | Sensit  | ivity and Dynamic Range                    | 58  |

|       | 2.4.1   | Sensitivity                                | 59  |

|       | 2.4.2   | Dynamic Range                              | 60  |

| 2.5   | Passiv  | ve Impedance Transformation                | 62  |

|       | 2.5.1   | Quality Factor                             | 63  |

|       | 2.5.2   | Series-to-Parallel Conversion              | 63  |

|       | 2.5.3   | Basic Matching Networks                    | 65  |

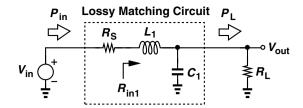

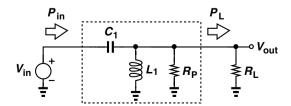

|       | 2.5.4   | Loss in Matching Networks                  | 69  |

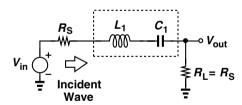

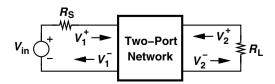

| 2.6   |         | ring Parameters                            | 71  |

| 2.7   |         | sis of Nonlinear Dynamic Systems           | 75  |

|       |         | Basic Considerations                       | 75  |

| 2.8   |         | ra Series                                  | 77  |

|       | 2.8.1   | Method of Nonlinear Currents               | 81  |

|       | erences |                                            | 86  |

| Prot  | olems   |                                            | 86  |

| СНАРТ | ER 3    | COMMUNICATION CONCEPTS                     | 91  |

| 3.1   | Gener   | ral Considerations                         | 91  |

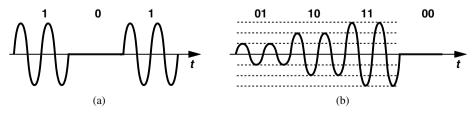

| 3.2   |         | g Modulation                               | 93  |

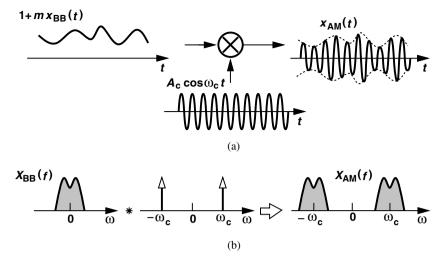

|       |         | Amplitude Modulation                       | 93  |

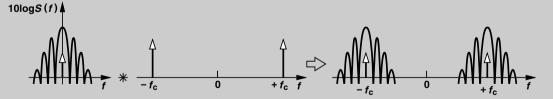

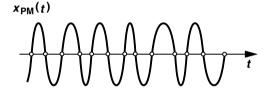

|       | 3.2.2   | Phase and Frequency Modulation             | 95  |

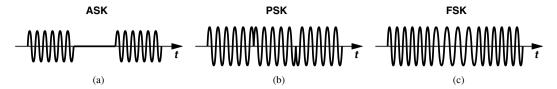

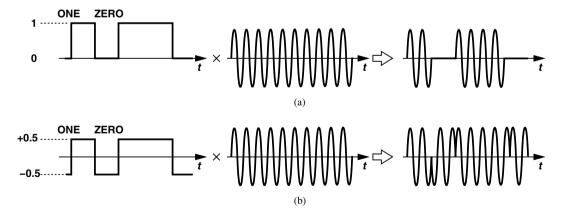

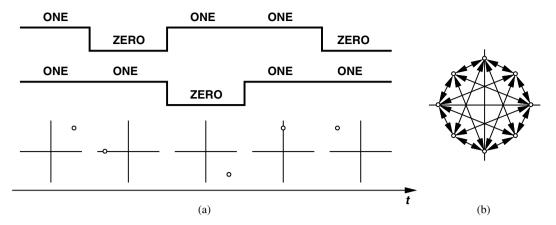

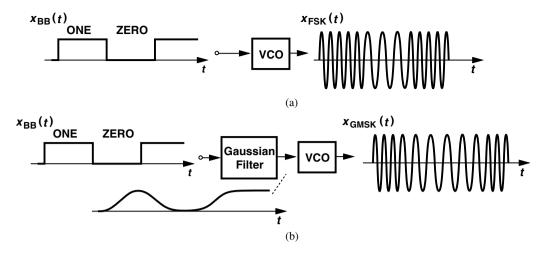

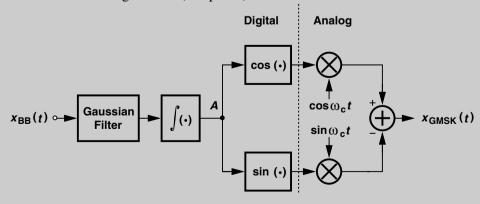

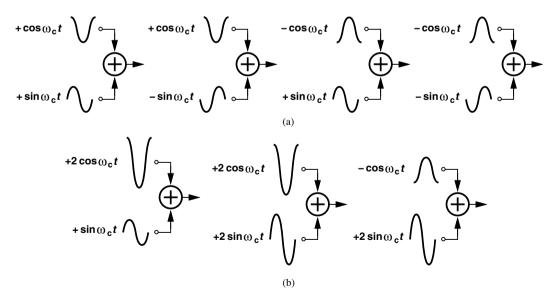

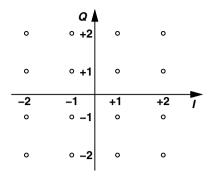

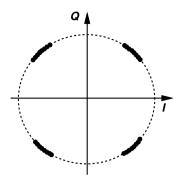

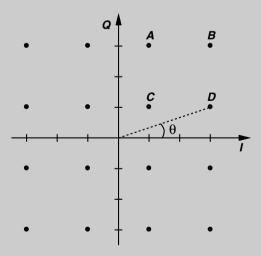

| 3.3   | Digita  | al Modulation                              | 99  |

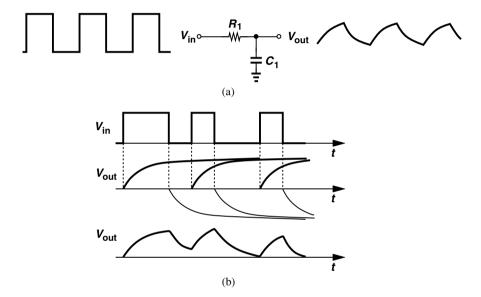

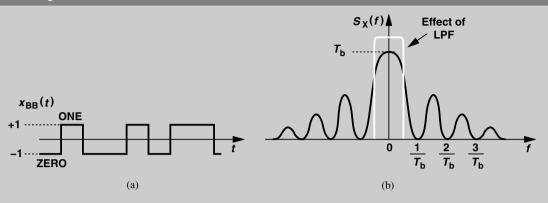

|       | _       | Intersymbol Interference                   | 101 |

|       | 3.3.2   |                                            | 105 |

|       | 3.3.3   |                                            | 107 |

|       | 3.3.4   | ~                                          | 112 |

|       | 3.3.5   |                                            | 114 |

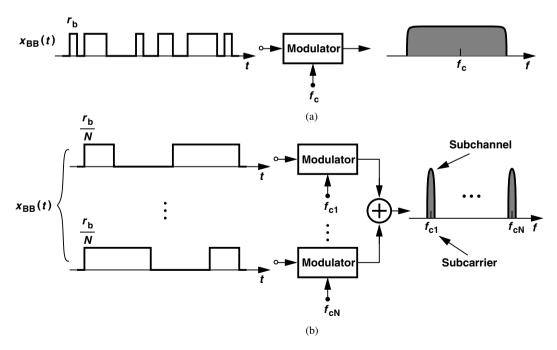

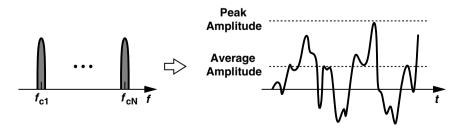

|       | 3.3.6   | Orthogonal Frequency Division Multiplexing | 115 |

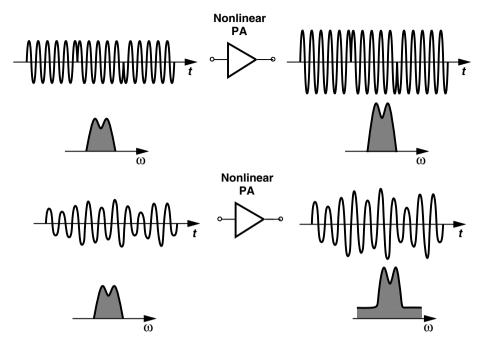

| 3.4   |         | ral Regrowth                               | 118 |

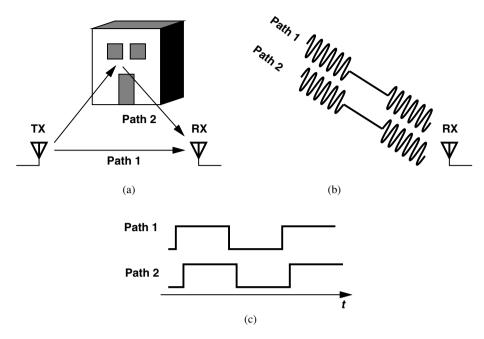

| 3.5   |         | e RF Communications                        | 119 |

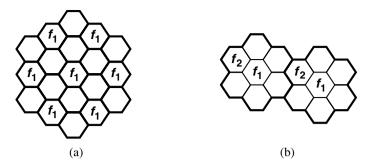

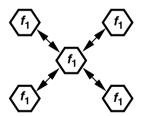

| 3.6   | Multip  | 123                                        |     |

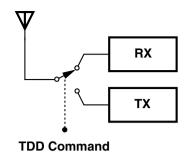

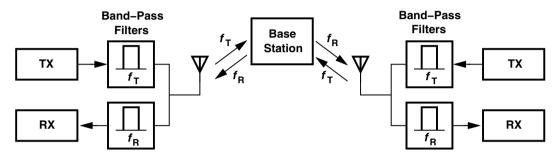

|       | 3.6.1   | Time and Frequency Division Duplexing      | 123 |

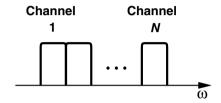

|       | 3.6.2   | Frequency-Division Multiple Access         | 125 |

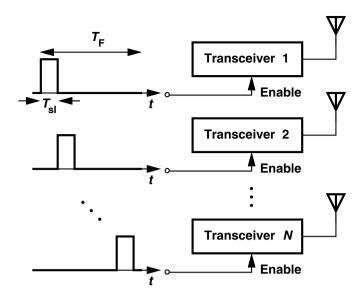

|       | 3.6.3   | Time-Division Multiple Access              | 125 |

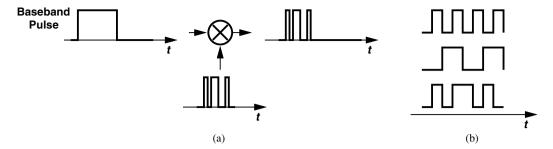

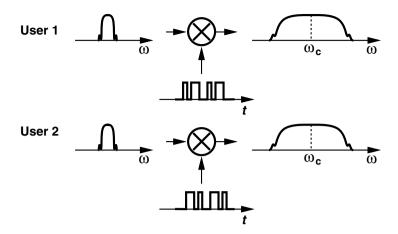

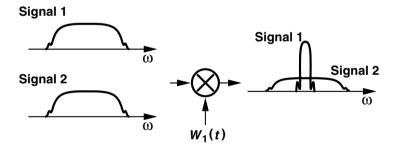

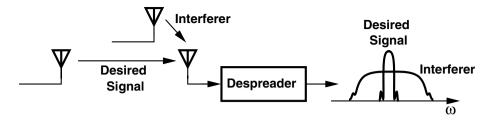

|       | 3.6.4   | Code-Division Multiple Access              | 126 |

| 3.7   |         | ess Standards                              | 130 |

| 2.7   | 3.7.1   | GSM                                        | 132 |

|       | 3.7.2   | IS-95 CDMA                                 | 137 |

|       | 3.7.3   | Wideband CDMA                              | 139 |

|       | 3.7.4   | Bluetooth                                  | 143 |

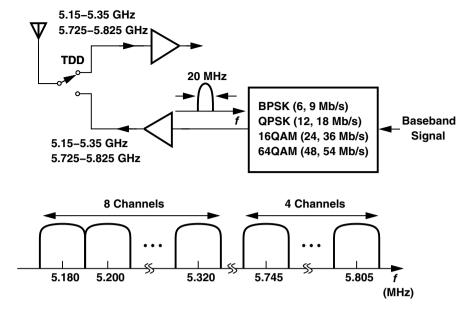

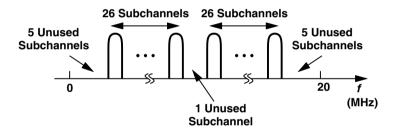

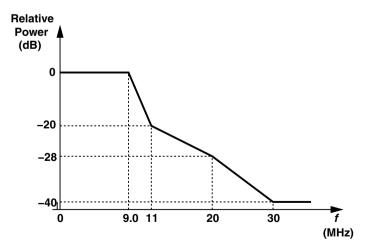

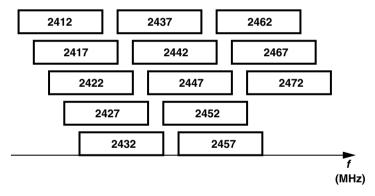

|       | 3.7.5   | IEEE802.11a/b/g                            | 147 |

|       | 5.1.5   | 1111002.114016                             | 1+/ |

Contents

|     | 3.8                | Appe           | endix I: Differential Phase Shift Keying | 151 |

|-----|--------------------|----------------|------------------------------------------|-----|

| ]   | Referer            | ices           |                                          | 152 |

| ]   | Probler            | ns             |                                          | 152 |

| СНА | PTER               | <b>4</b>       | TRANSCEIVER ARCHITECTURES                | 155 |

|     |                    |                | eral Considerations                      | 155 |

| 4   |                    |                | iver Architectures                       | 160 |

|     |                    | 4.2.1          | 3                                        | 160 |

|     |                    | 4.2.2          |                                          | 171 |

|     |                    |                | Direct-Conversion Receivers              | 179 |

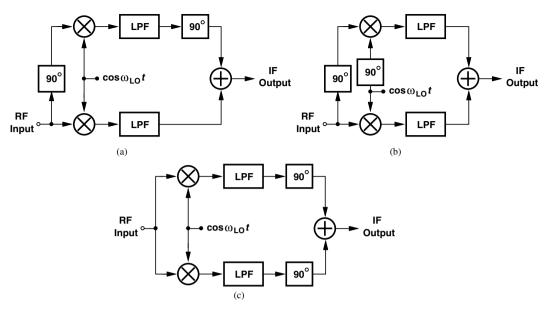

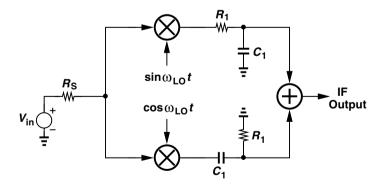

|     |                    |                | Image-Reject Receivers                   | 200 |

|     | 4                  | 4.2.5          | Low-IF Receivers                         | 214 |

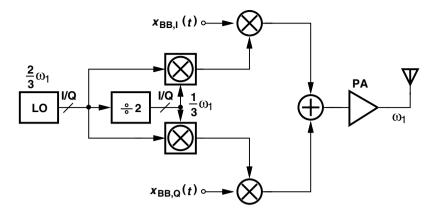

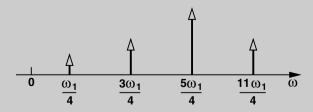

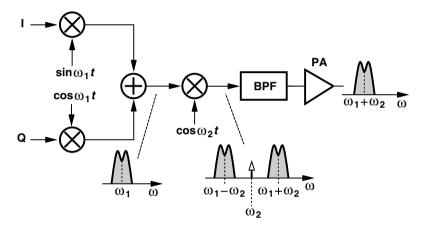

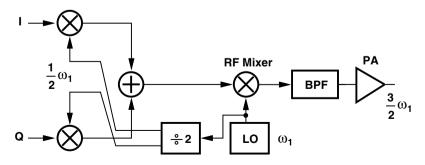

| 4   | 4.3                | Trans          | smitter Architectures                    | 226 |

|     | 4                  | 4.3.1          | General Considerations                   | 226 |

|     |                    |                | Direct-Conversion Transmitters           | 227 |

|     | 4                  | 4.3.3          | Modern Direct-Conversion Transmitters    | 238 |

|     | 4                  | 4.3.4          | Heterodyne Transmitters                  | 244 |

|     | 4                  | 4.3.5          | Other TX Architectures                   | 248 |

| 4   | 4.4                | OOK            | Transceivers                             | 248 |

| ]   | Referer            | nces           |                                          | 249 |

| ]   | Probler            | ns             |                                          | 250 |

| СНА | PTER               | 2 5            | LOW-NOISE AMPLIFIERS                     | 255 |

|     |                    |                | eral Considerations                      | 255 |

|     |                    |                | lem of Input Matching                    | 263 |

|     |                    |                | Topologies                               | 266 |

| •   |                    | 5.3.1          | · ·                                      | 266 |

|     |                    | 5.3.2          |                                          | 269 |

|     |                    | 5.3.3          | <u>c</u>                                 | 272 |

|     |                    | 5.3.4          | E                                        | 284 |

|     |                    |                | Variants of Common-Gate LNA              | 296 |

|     |                    | 5.3.6          |                                          | 300 |

|     |                    |                | Reactance-Cancelling LNAs                | 303 |

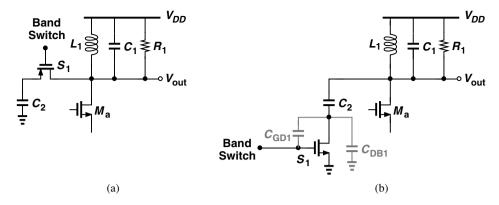

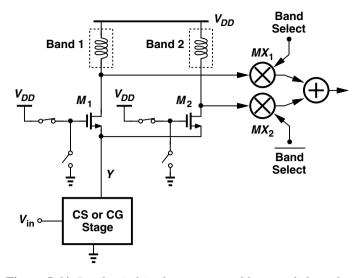

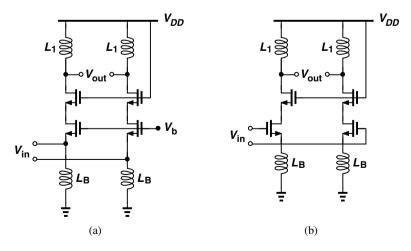

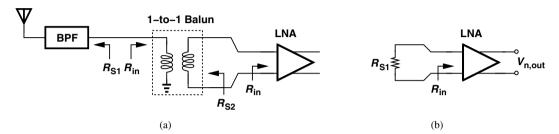

|     |                    |                | Switching                                | 305 |

|     |                    |                | Switching                                | 312 |

|     |                    |                | -IP <sub>2</sub> LNAs                    | 313 |

|     |                    | 5.6.1          |                                          | 314 |

|     |                    | 5.6.2          |                                          | 323 |

|     |                    |                | inearity Calculations                    | 325 |

|     |                    | 5.7.1          | •                                        | 325 |

|     |                    | 5.7.1<br>5.7.2 | e                                        | 329 |

|     |                    | 5.7.2<br>5.7.3 | e e                                      | 331 |

|     |                    | 5.7.3<br>5.7.4 |                                          | 332 |

| ,   | Referer            |                | Degenerated Differential Pall            | 333 |

|     | Reielei<br>Probler |                |                                          | 333 |

|     |                    |                |                                          |     |

X Contents

| СНАРТ | <b>ER 6</b>            | MIXERS                                       | 337        |  |

|-------|------------------------|----------------------------------------------|------------|--|

| 6.1   | Gener                  | ral Considerations                           | 337        |  |

|       | 6.1.1                  | Performance Parameters                       | 338        |  |

|       | 6.1.2                  | Mixer Noise Figures                          | 343        |  |

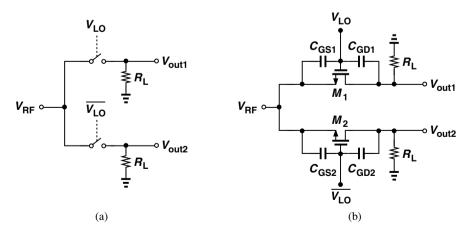

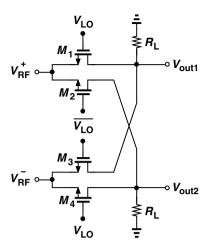

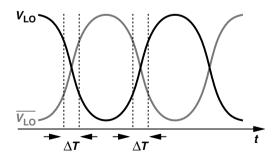

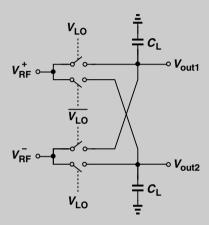

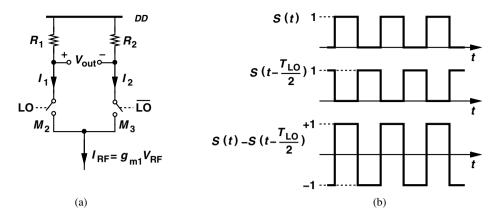

|       | 6.1.3                  | Single-Balanced and Double-Balanced Mixers   | 348        |  |

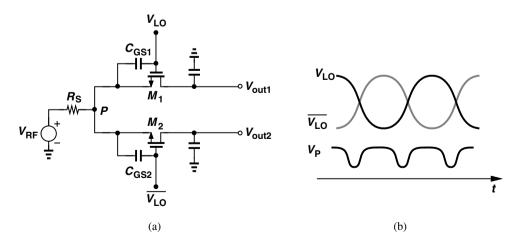

| 6.2   | Passiv                 | ve Downconversion Mixers                     | 350        |  |

|       |                        | Gain                                         | 350        |  |

|       |                        | LO Self-Mixing                               | 357        |  |

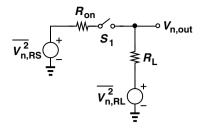

|       | 6.2.3                  | Noise                                        | 357        |  |

|       |                        | Input Impedance                              | 364        |  |

|       | 6.2.5                  |                                              | 366        |  |

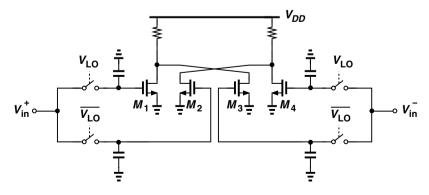

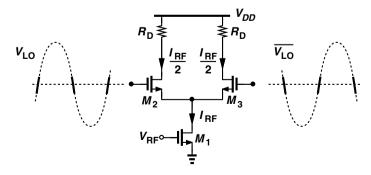

| 6.3   |                        | e Downconversion Mixers                      | 368        |  |

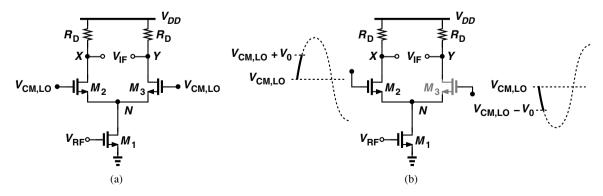

|       |                        | Conversion Gain                              | 370        |  |

|       |                        | Noise in Active Mixers                       | 377        |  |

|       |                        | Linearity                                    | 387        |  |

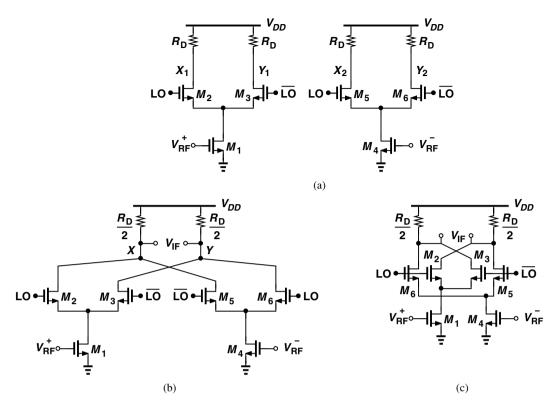

| 6.4   | _                      | ved Mixer Topologies                         | 393        |  |

|       | 6.4.1                  | 1                                            | 393        |  |

|       |                        | Active Mixers with Enhanced Transconductance | 394        |  |

|       |                        | Active Mixers with High IP <sub>2</sub>      | 397        |  |

|       | 6.4.4                  |                                              | 405        |  |

| 6.5   | •                      | nversion Mixers                              | 408        |  |

|       | 6.5.1                  | 1                                            | 408        |  |

| ъ.    | 6.5.2                  | Upconversion Mixer Topologies                | 409<br>424 |  |

|       | References             |                                              |            |  |

| Pro   | blems                  |                                              | 425        |  |

| СНАРТ | ER 7                   | PASSIVE DEVICES                              | 429        |  |

| 7.1   | Gener                  | ral Considerations                           | 429        |  |

| 7.2   | Induct                 | tors                                         | 431        |  |

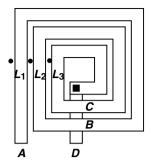

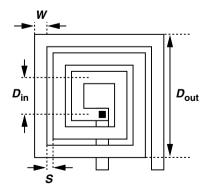

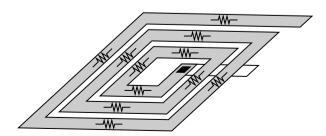

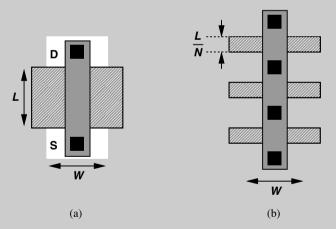

|       | 7.2.1                  | Basic Structure                              | 431        |  |

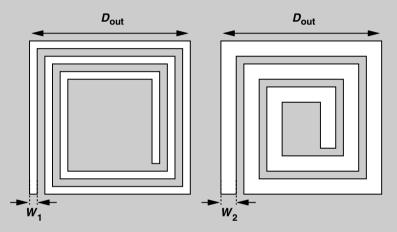

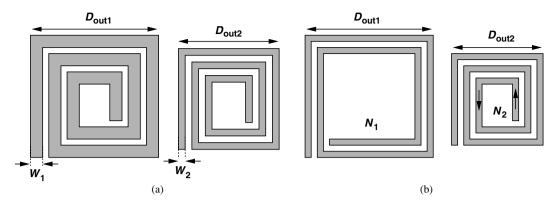

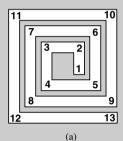

|       | 7.2.2                  | Inductor Geometries                          | 435        |  |

|       | 7.2.3                  | Inductance Equations                         | 436        |  |

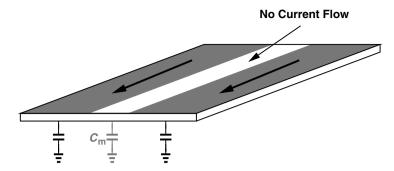

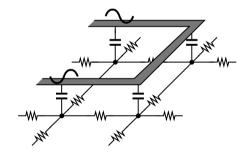

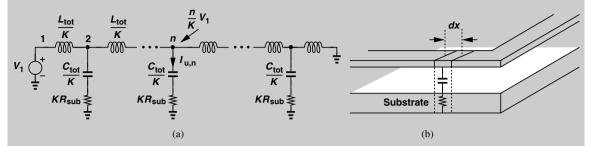

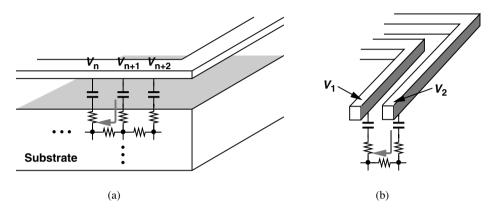

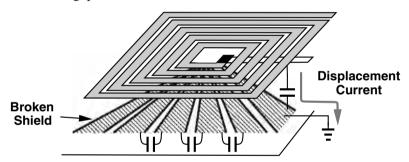

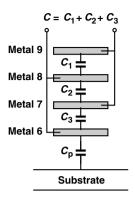

|       | 7.2.4                  | Parasitic Capacitances                       | 439        |  |

|       | 7.2.5                  | Loss Mechanisms                              | 444        |  |

|       | 7.2.6                  | Inductor Modeling                            | 455        |  |

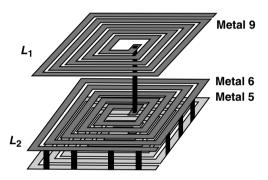

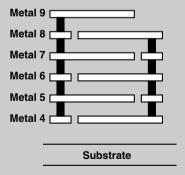

|       | 7.2.7                  | Alternative Inductor Structures              | 460        |  |

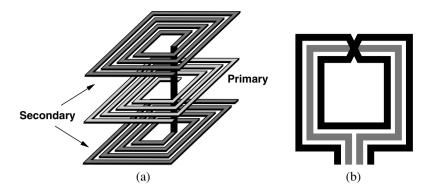

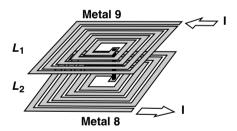

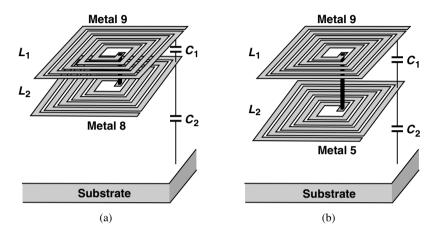

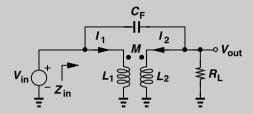

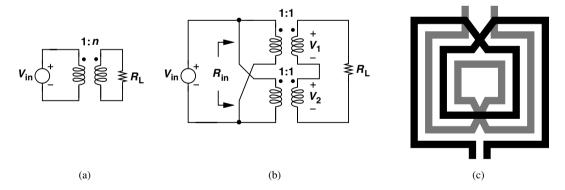

| 7.3   | Transf                 | formers                                      | 470        |  |

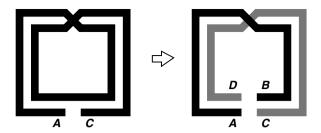

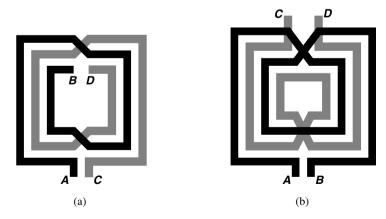

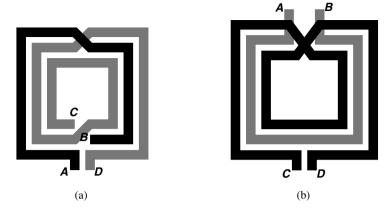

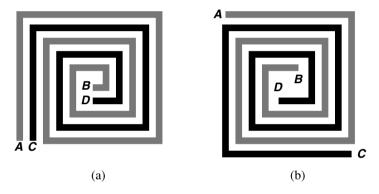

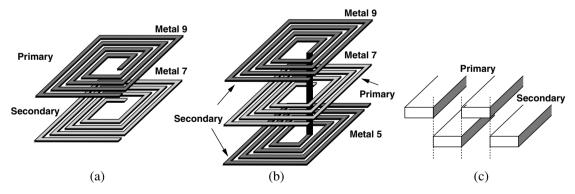

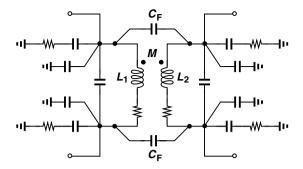

|       | 7.3.1                  | Transformer Structures                       | 470        |  |

|       | 7.3.2                  | Effect of Coupling Capacitance               | 475        |  |

|       | 7.3.3                  | Transformer Modeling                         | 475        |  |

| 7.4   | 7.4 Transmission Lines |                                              | 476        |  |

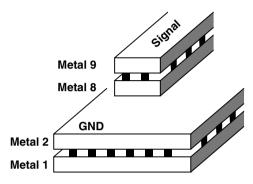

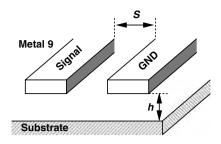

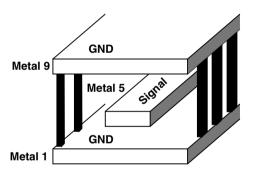

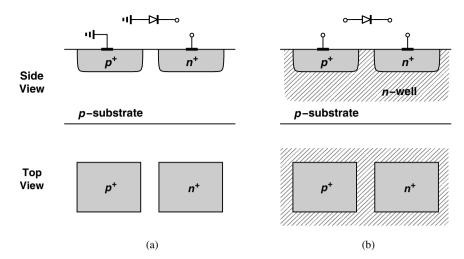

|       | 7.4.1                  | T-Line Structures                            | 478        |  |

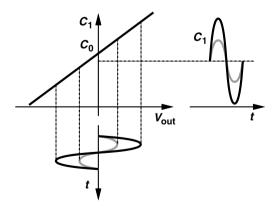

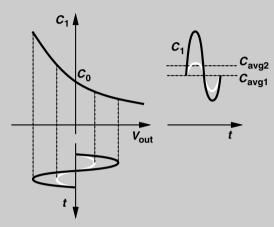

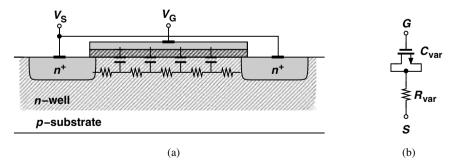

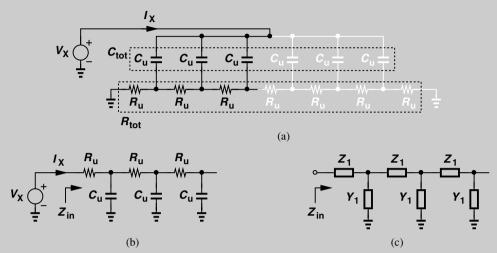

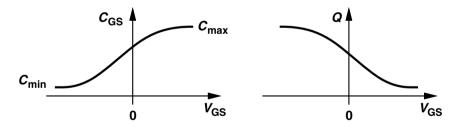

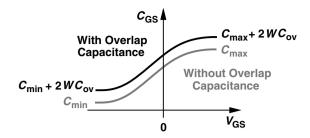

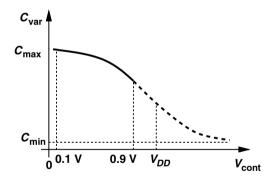

| 7.5   | Varact                 | tors                                         | 483        |  |

| 7.6   | Const                  | ant Capacitors                               | 490        |  |

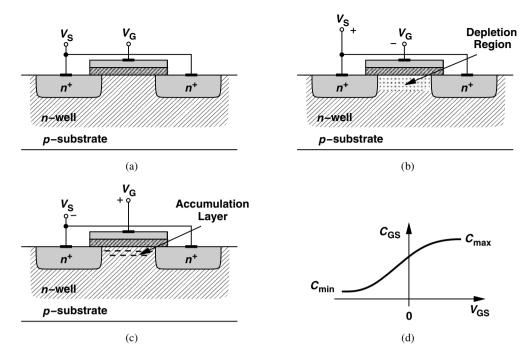

|       | 7.6.1                  | MOS Capacitors                               | 491        |  |

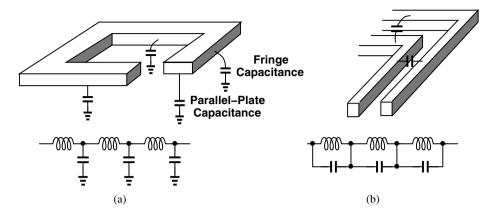

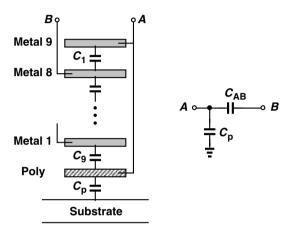

|       | 762                    | Metal-Plate Capacitors                       | 493        |  |

*Contents* xi

| Refe   | References                                       |                   |  |

|--------|--------------------------------------------------|-------------------|--|

|        | Problems                                         |                   |  |

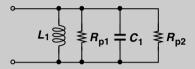

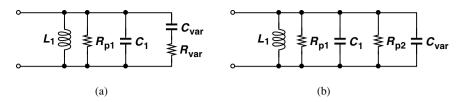

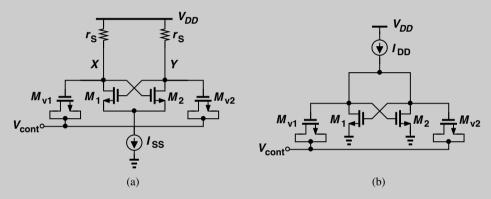

| CHAPTI | ER 8 OSCILLATORS                                 | 497               |  |

| 8.1    | Performance Parameters                           | <b>497</b><br>497 |  |

| 8.2    | Basic Principles                                 | 501               |  |

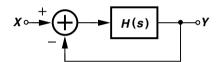

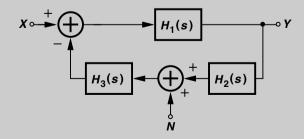

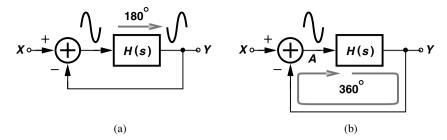

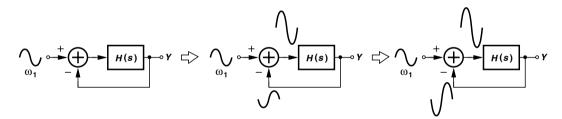

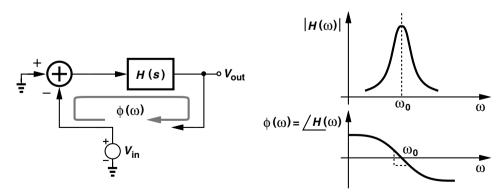

| 0.2    | 8.2.1 Feedback View of Oscillators               | 502               |  |

|        | 8.2.2 One-Port View of Oscillators               | 508               |  |

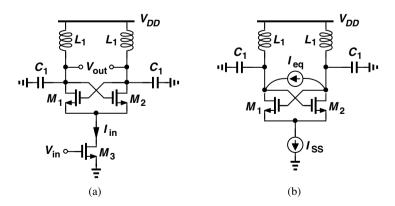

| 8.3    | Cross-Coupled Oscillator                         | 511               |  |

| 8.4    | Three-Point Oscillators                          | 517               |  |

| 8.5    | Voltage-Controlled Oscillators                   | 518               |  |

| 0.5    | 8.5.1 Tuning Range Limitations                   | 521               |  |

|        | 8.5.2 Effect of Varactor Q                       | 522               |  |

| 8.6    | LC VCOs with Wide Tuning Range                   | 524               |  |

| 0.0    | 8.6.1 VCOs with Continuous Tuning                | 524               |  |

|        | 8.6.2 Amplitude Variation with Frequency Tuning  | 532               |  |

|        | 8.6.3 Discrete Tuning                            | 532               |  |

| 8.7    | Phase Noise                                      | 536               |  |

|        | 8.7.1 Basic Concepts                             | 536               |  |

|        | 8.7.2 Effect of Phase Noise                      | 539               |  |

|        | 8.7.3 Analysis of Phase Noise: Approach I        | 544               |  |

|        | 8.7.4 Analysis of Phase Noise: Approach II       | 557               |  |

|        | 8.7.5 Noise of Bias Current Source               | 565               |  |

|        | 8.7.6 Figures of Merit of VCOs                   | 570               |  |

| 8.8    | Design Procedure                                 | 571               |  |

|        | 8.8.1 Low-Noise VCOs                             | 573               |  |

| 8.9    | LO Interface                                     | 575               |  |

| 8.10   | Mathematical Model of VCOs                       | 577               |  |

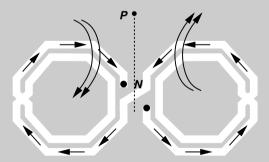

| 8.11   | Quadrature Oscillators                           | 581               |  |

|        | 8.11.1 Basic Concepts                            | 581               |  |

|        | 8.11.2 Properties of Coupled Oscillators         | 584               |  |

|        | 8.11.3 Improved Quadrature Oscillators           | 589               |  |

| 8.12   | Appendix I: Simulation of Quadrature Oscillators | 592               |  |

| Refe   | rences                                           | 593               |  |

| Prob   | lems                                             | 594               |  |

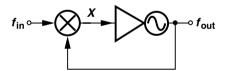

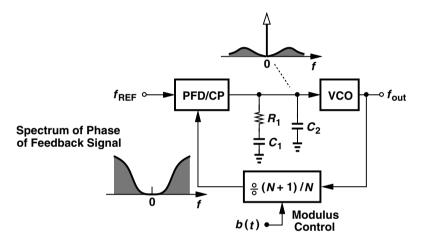

| CHAPTI | ER 9 PHASE-LOCKED LOOPS                          | 597               |  |

| 9.1    | Basic Concepts                                   | 597               |  |

|        | 9.1.1 Phase Detector                             | 597               |  |

| 9.2    | Type-I PLLs                                      | 600               |  |

|        | 9.2.1 Alignment of a VCO's Phase                 | 600               |  |

|        | 9.2.2 Simple PLL                                 | 601               |  |

|        | 9.2.3 Analysis of Simple PLL                     | 603               |  |

|        | 9.2.4 Loop Dynamics                              | 606               |  |

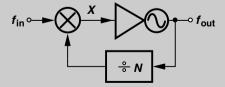

|        | 9.2.5 Frequency Multiplication                   | 609               |  |

|        | 9.2.6 Drawbacks of Simple PLL                    | 611               |  |

Xii Contents

|    | 9.3        | Type-II | PLLs                                         | 611        |

|----|------------|---------|----------------------------------------------|------------|

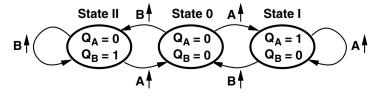

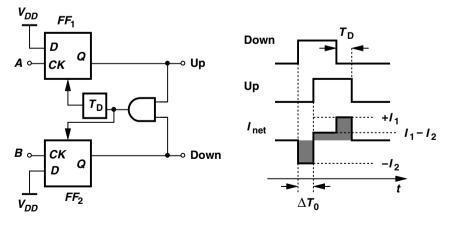

|    |            | 9.3.1   | Phase/Frequency Detectors                    | 612        |

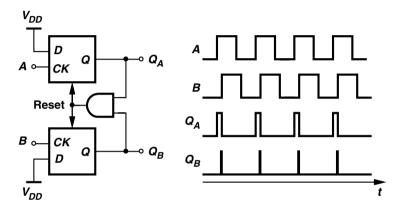

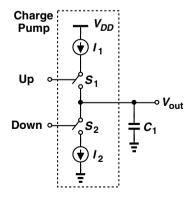

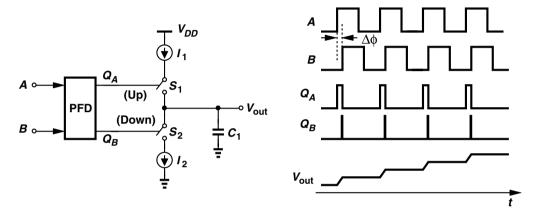

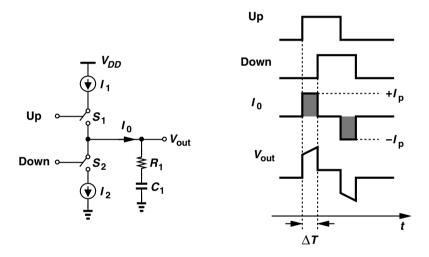

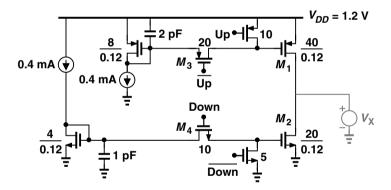

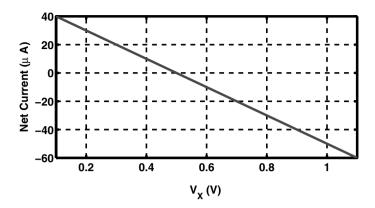

|    |            | 9.3.2   | Charge Pumps                                 | 614        |

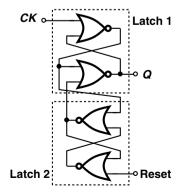

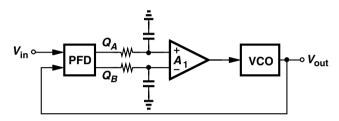

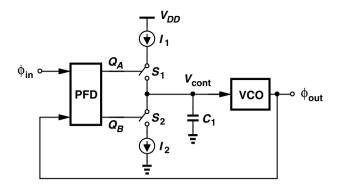

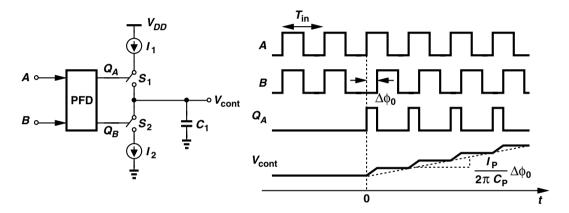

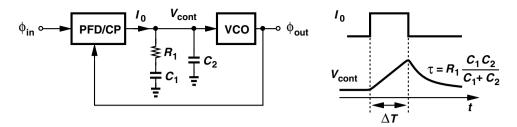

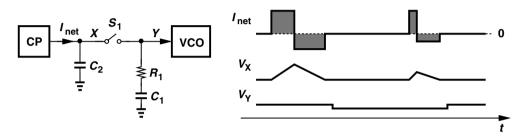

|    |            | 9.3.3   | Charge-Pump PLLs                             | 615        |

|    |            | 9.3.4   | Transient Response                           | 620        |

|    |            | 9.3.5   | Limitations of Continuous-Time Approximation | 622        |

|    |            | 9.3.6   | Frequency-Multiplying CPPLL                  | 623        |

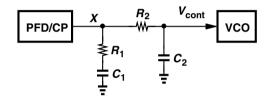

|    |            | 9.3.7   | Higher-Order Loops                           | 625        |

|    | 9.4        | PFD/CI  | P Nonidealities                              | 627        |

|    |            | 9.4.1   | Up and Down Skew and Width Mismatch          | 627        |

|    |            | 9.4.2   | Voltage Compliance                           | 630        |

|    |            | 9.4.3   | Charge Injection and Clock Feedthrough       | 630        |

|    |            | 9.4.4   | Random Mismatch between Up and Down Currents | 632        |

|    |            |         | Channel-Length Modulation                    | 633        |

|    |            |         | Circuit Techniques                           | 634        |

|    | 9.5        |         | Noise in PLLs                                | 638        |

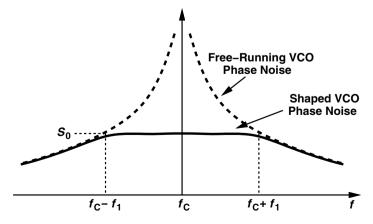

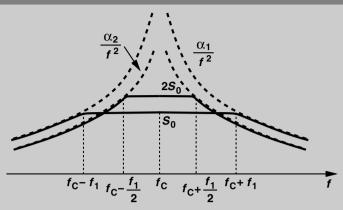

|    |            |         | VCO Phase Noise                              | 638        |

|    |            | 9.5.2   | Reference Phase Noise                        | 643        |

|    | 9.6        | •       | andwidth                                     | 645        |

|    | 9.7        | _       | Procedure                                    | 646        |

|    | 9.8        |         | lix I: Phase Margin of Type-II PLLs          | 647<br>651 |

|    | References |         |                                              |            |

|    | Proble     | ems     |                                              | 652        |

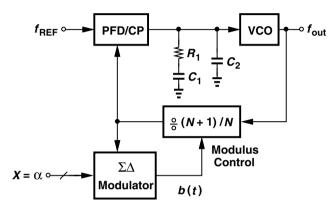

| CH | APTE       | R 10    | INTEGER-N FREQUENCY SYNTHESIZERS             | 655        |

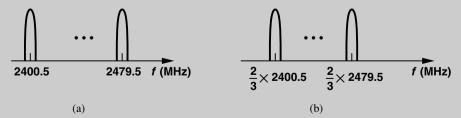

|    | 10.1       |         | al Considerations                            | 655        |

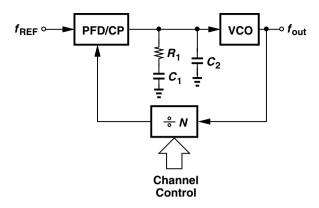

|    | 10.2       | Basic   | Integer-N Synthesizer                        | 659        |

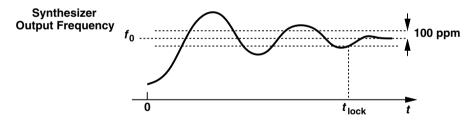

|    | 10.3       | Settlin | ng Behavior                                  | 661        |

|    | 10.4       | Spur F  | Reduction Techniques                         | 664        |

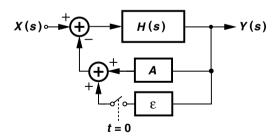

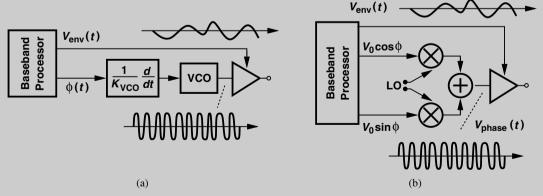

|    | 10.5       | PLL-E   | Based Modulation                             | 667        |

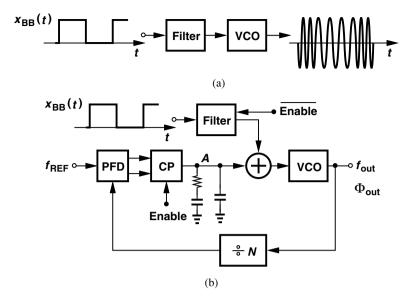

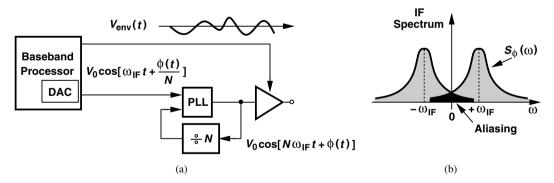

|    |            | 10.5.1  | In-Loop Modulation                           | 667        |

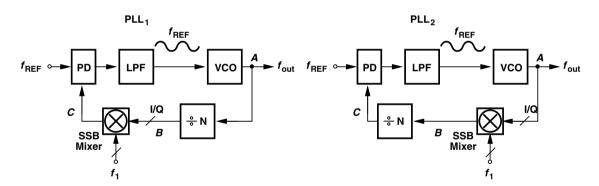

|    |            | 10.5.2  | Modulation by Offset PLLs                    | 670        |

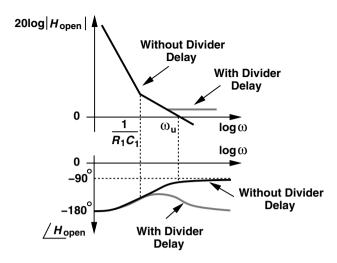

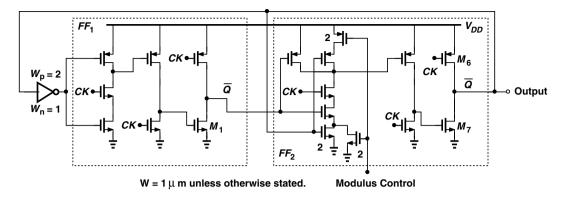

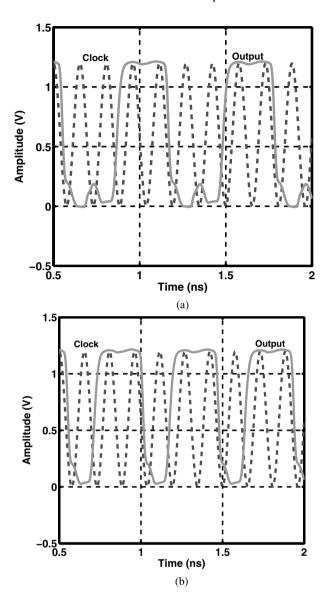

|    | 10.6       | Divide  | er Design                                    | 673        |

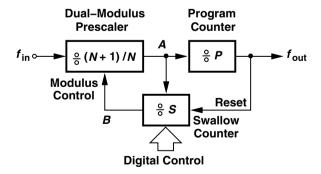

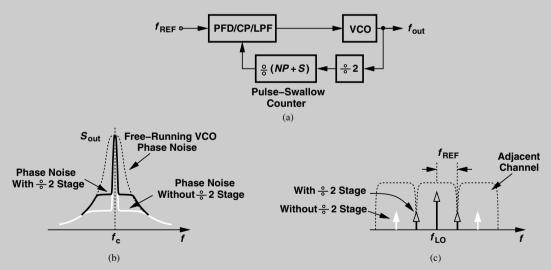

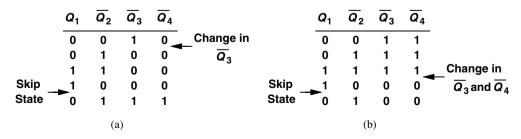

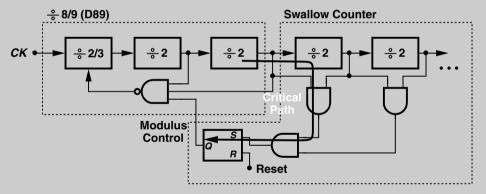

|    |            | 10.6.1  | Pulse Swallow Divider                        | 674        |

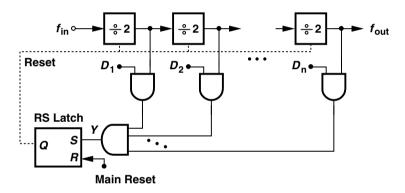

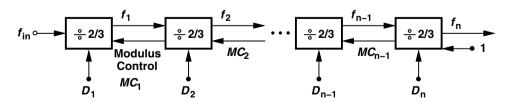

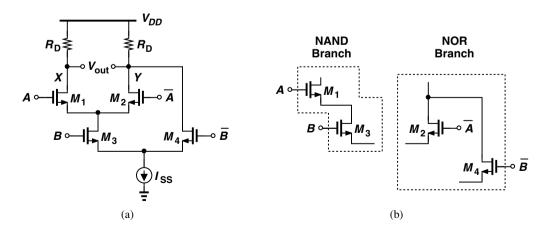

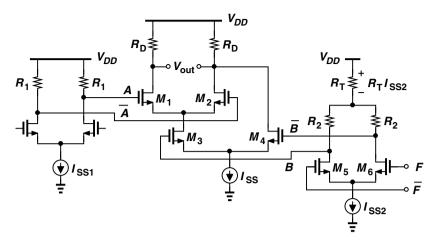

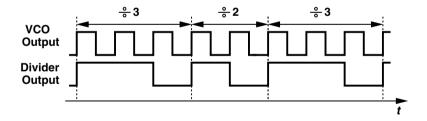

|    |            | 10.6.2  | Dual-Modulus Dividers                        | 677        |

|    |            | 10.6.3  | Choice of Prescaler Modulus                  | 682        |

|    |            | 10.6.4  | $\mathcal{E}$                                | 683        |

|    |            | 10.6.5  |                                              | 699        |

|    |            | 10.6.6  | 3                                            | 707        |

|    |            | 10.6.7  | Divider Delay and Phase Noise                | 709        |

|    | Refere     |         |                                              | 712        |

|    | Proble     | ems     |                                              | 713        |

Contents

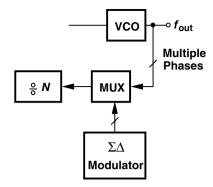

| <b>CHAPTE</b> | R 11 F   | RACTIONAL-N SYNTHESIZERS                | 715 |

|---------------|----------|-----------------------------------------|-----|

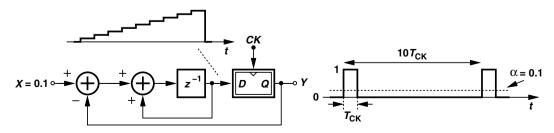

| 11.1          | Basic C  | Concepts                                | 715 |

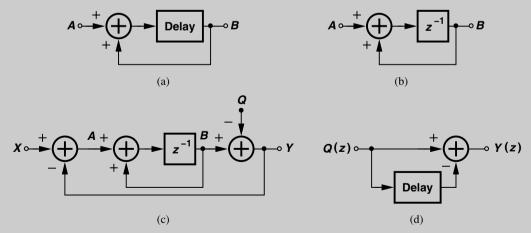

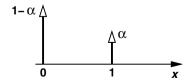

| 11.2          | Randor   | mization and Noise Shaping              | 718 |

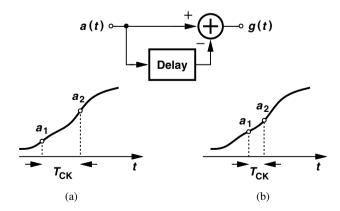

|               | 11.2.1   | Modulus Randomization                   | 718 |

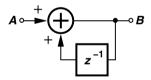

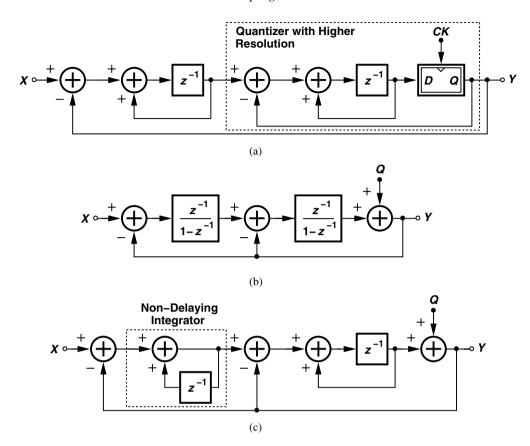

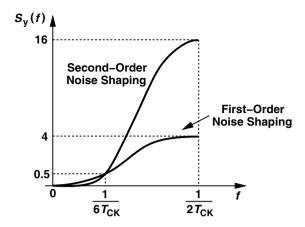

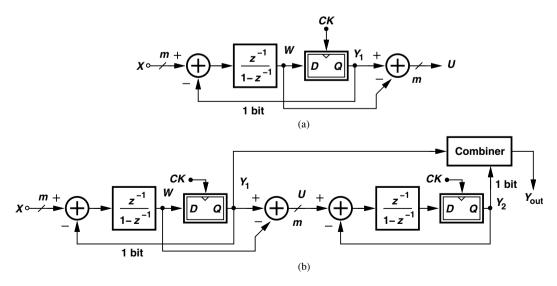

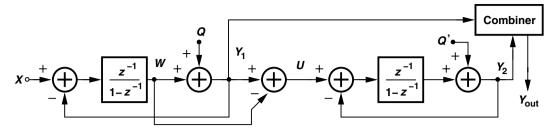

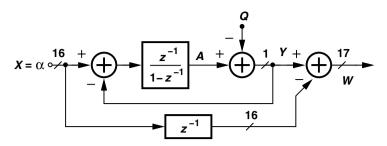

|               | 11.2.2   | Basic Noise Shaping                     | 722 |

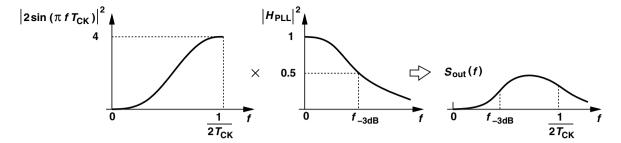

|               | 11.2.3   | Higher-Order Noise Shaping              | 728 |

|               | 11.2.4   | Problem of Out-of-Band Noise            | 732 |

|               | 11.2.5   | Effect of Charge Pump Mismatch          | 733 |

| 11.3          | Quantiz  | zation Noise Reduction Techniques       | 738 |

|               | 11.3.1   | DAC Feedforward                         | 738 |

|               |          | Fractional Divider                      | 742 |

|               |          | Reference Doubling                      | 743 |

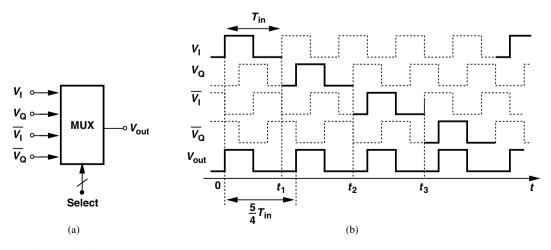

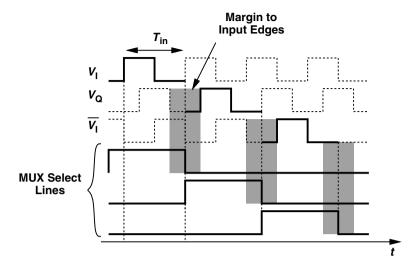

|               |          | Multiphase Frequency Division           | 745 |

| 11.4          |          | dix I: Spectrum of Quantization Noise   | 748 |

| Refere        |          |                                         | 749 |

| Proble        | ems      |                                         | 749 |

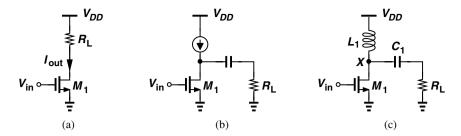

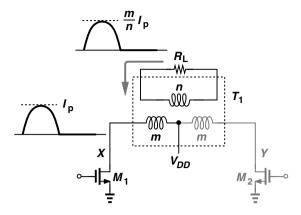

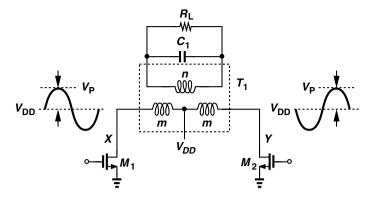

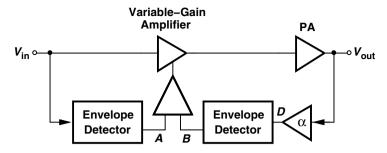

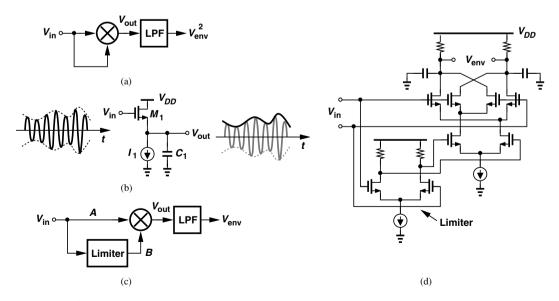

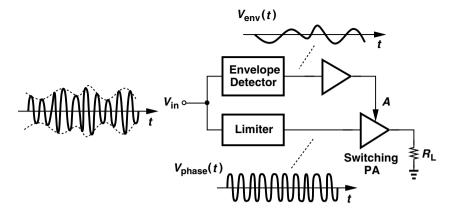

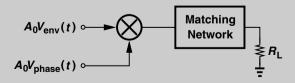

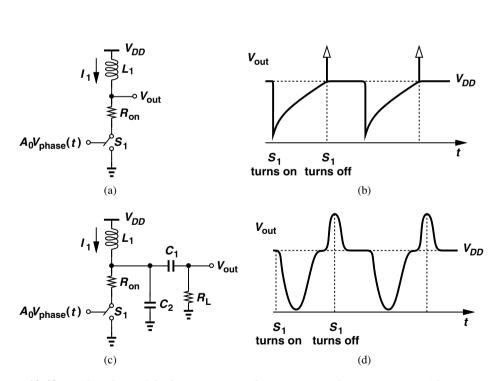

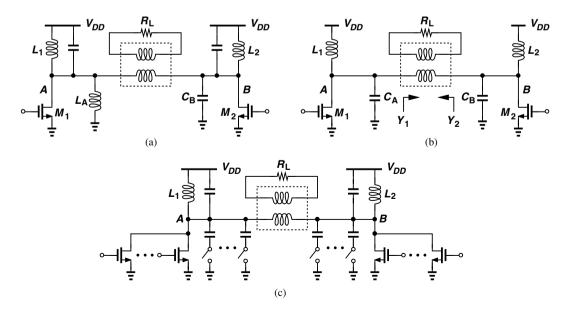

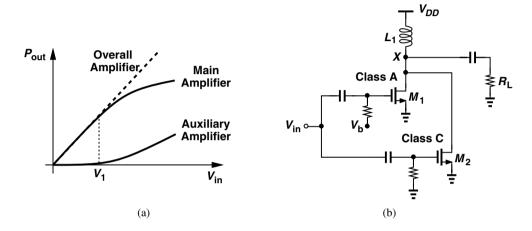

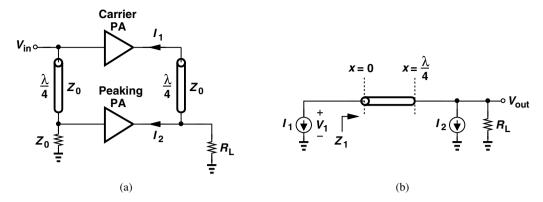

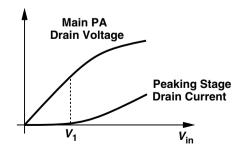

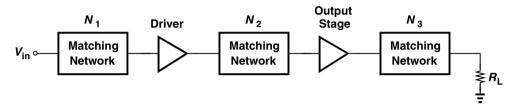

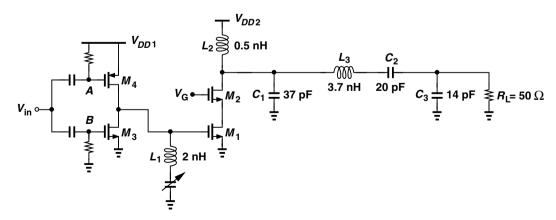

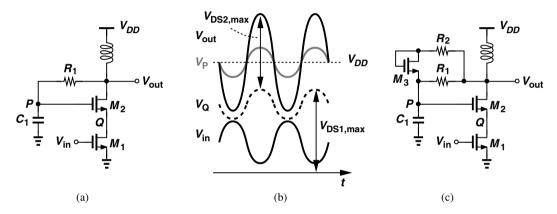

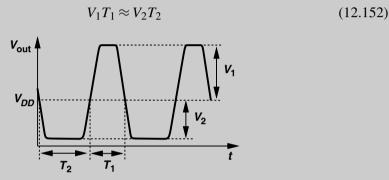

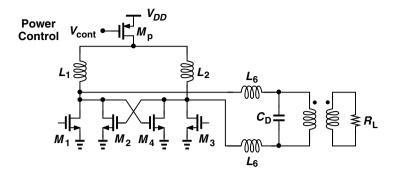

| СНАРТЕ        | R 12 P   | POWER AMPLIFIERS                        | 751 |

| 12.1          | Genera   | l Considerations                        | 751 |

|               | 12.1.1   | Effect of High Currents                 | 754 |

|               | 12.1.2   |                                         | 755 |

|               | 12.1.3   | Linearity                               | 756 |

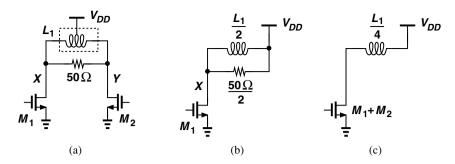

|               | 12.1.4   | Single-Ended and Differential PAs       | 758 |

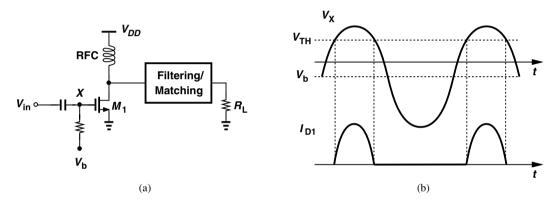

| 12.2          | Classifi | ication of Power Amplifiers             | 760 |

|               | 12.2.1   | Class A Power Amplifiers                | 760 |

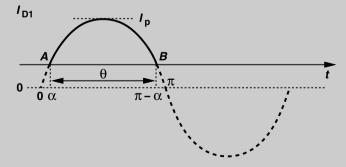

|               | 12.2.2   | Class B Power Amplifiers                | 764 |

|               | 12.2.3   | Class C Power Amplifiers                | 768 |

| 12.3          | High-E   | Efficiency Power Amplifiers             | 770 |

|               | 12.3.1   | Class A Stage with Harmonic Enhancement | 771 |

|               | 12.3.2   | Class E Stage                           | 772 |

|               | 12.3.3   | Class F Power Amplifiers                | 775 |

| 12.4          | Cascod   | le Output Stages                        | 776 |

| 12.5          | Large-S  | Signal Impedance Matching               | 780 |

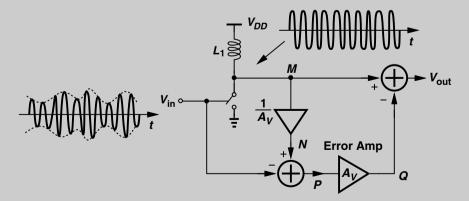

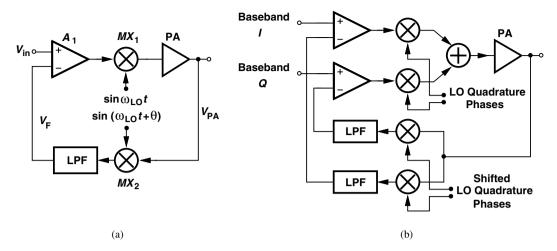

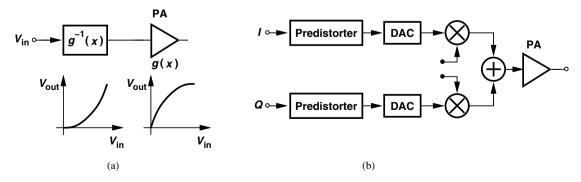

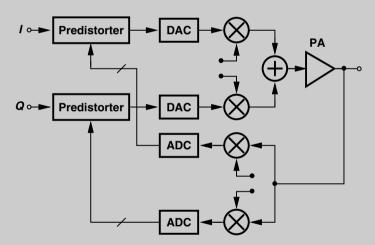

| 12.6          | Basic L  | Linearization Techniques                | 782 |

|               | 12.6.1   | Feedforward                             | 783 |

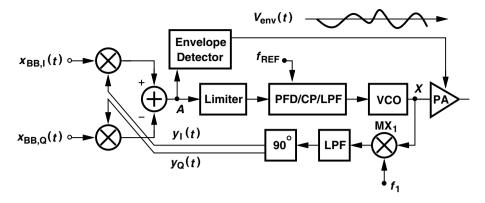

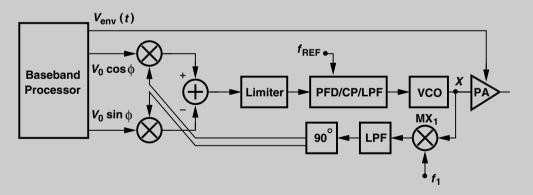

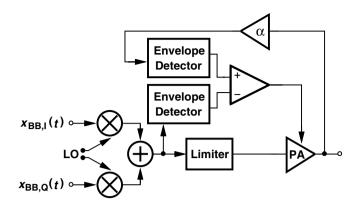

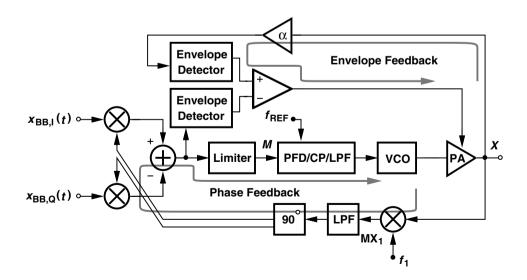

|               | 12.6.2   | Cartesian Feedback                      | 786 |

|               | 12.6.3   | Predistortion                           | 787 |

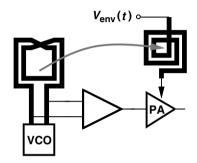

|               | 12.6.4   | Envelope Feedback                       | 788 |

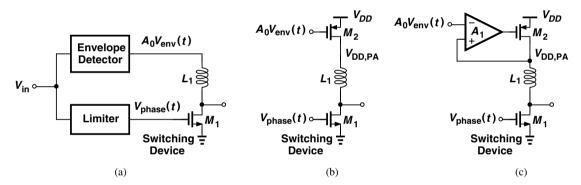

| 12.7          |          | Modulation                              | 790 |

|               | 12.7.1   | Basic Idea                              | 790 |

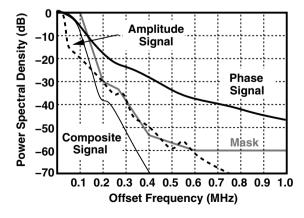

|               | 12.7.2   | Polar Modulation Issues                 | 793 |

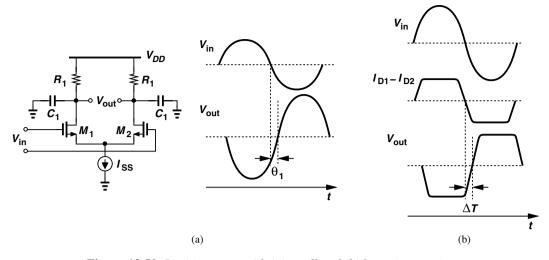

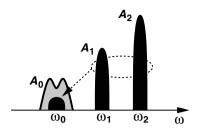

|               | 12.7.3   | Improved Polar Modulation               | 796 |

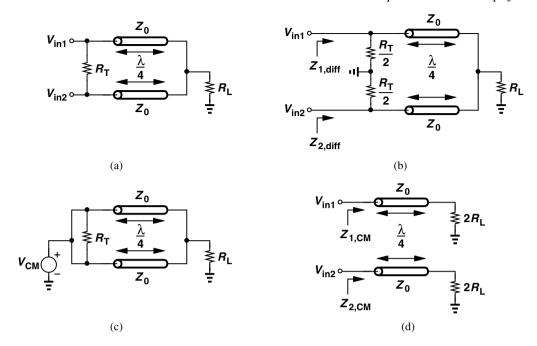

| 12.8   | Outpha   | asing                      | 802 |

|--------|----------|----------------------------|-----|

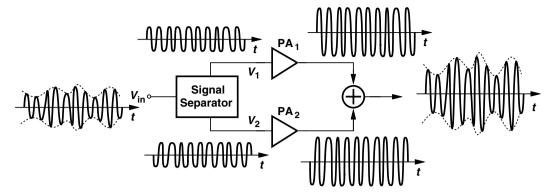

|        | 12.8.1   | Basic Idea                 | 802 |

|        | 12.8.2   | Outphasing Issues          | 805 |

| 12.9   | Dohert   | y Power Amplifier          | 811 |

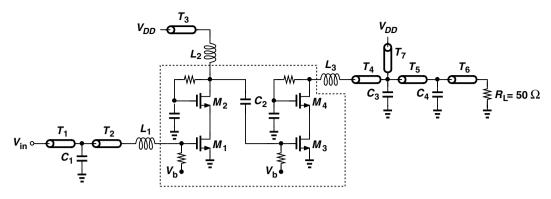

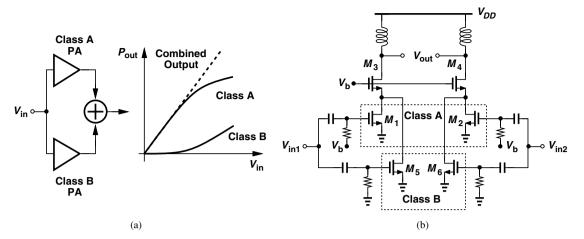

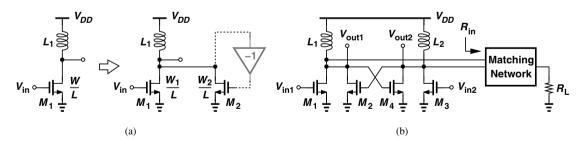

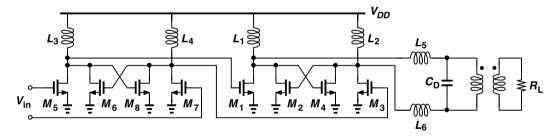

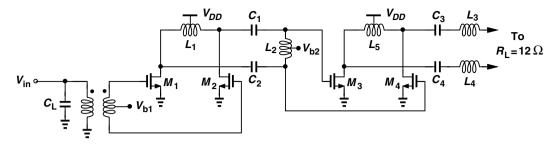

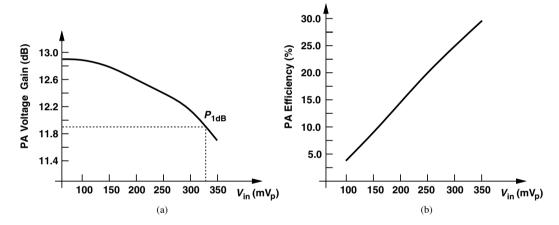

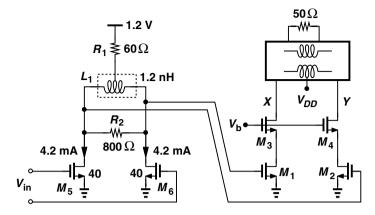

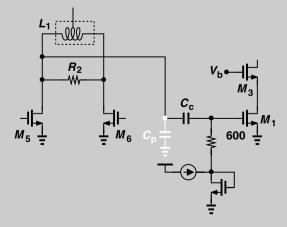

| 12.10  | ) Design | Examples                   | 814 |

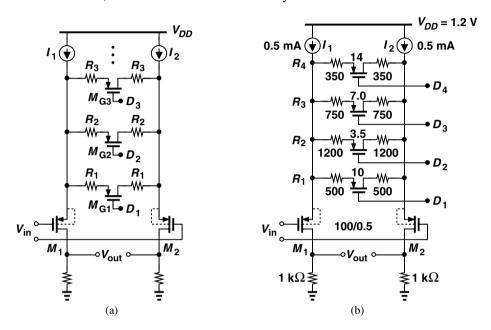

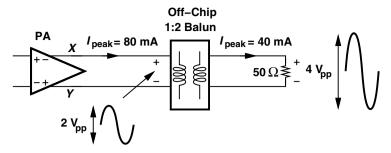

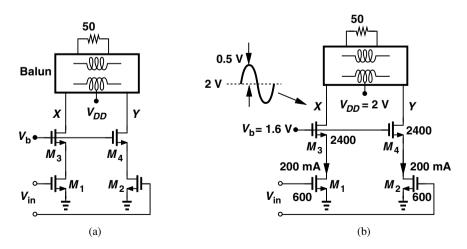

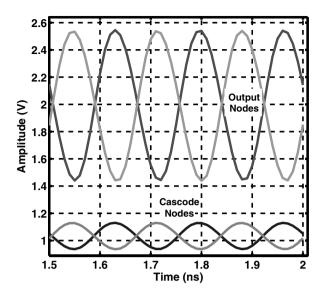

|        | 12.10.1  | Cascode PA Examples        | 815 |

|        |          | Positive-Feedback PAs      | 819 |

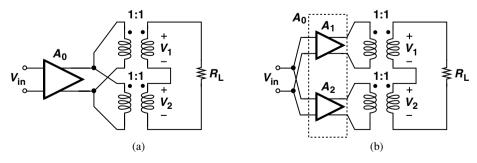

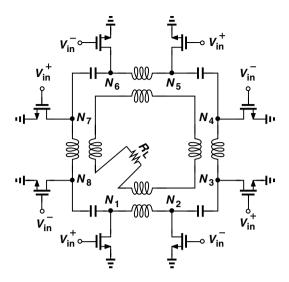

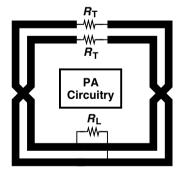

|        | 12.10.3  | PAs with Power Combining   | 821 |

|        | 12.10.4  | Polar Modulation PAs       | 824 |

|        | 12.10.5  | Outphasing PA Example      | 826 |

| Refe   | rences   |                            | 830 |

| Prob   | lems     |                            | 831 |

| СНАРТІ | ER 13 T  | TRANSCEIVER DESIGN EXAMPLE | 833 |

| 13.1   | System   | n-Level Considerations     | 833 |

|        | 13.1.1   | Receiver                   | 834 |

|        |          | Transmitter                | 838 |

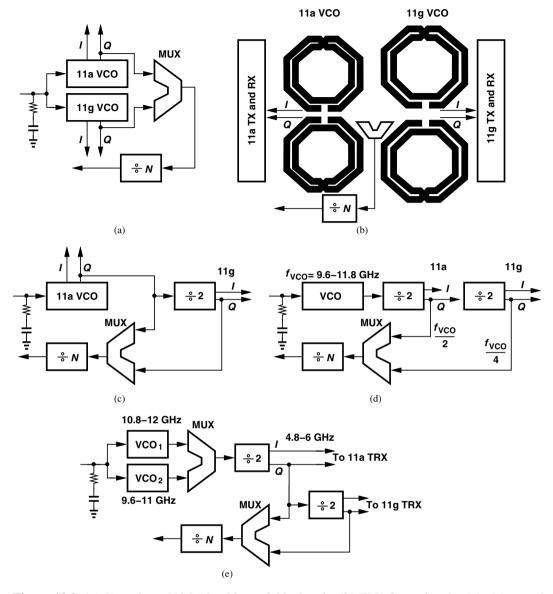

|        | 13.1.3   | Frequency Synthesizer      | 840 |

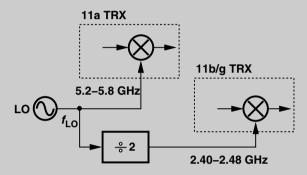

|        | 13.1.4   | Frequency Planning         | 844 |

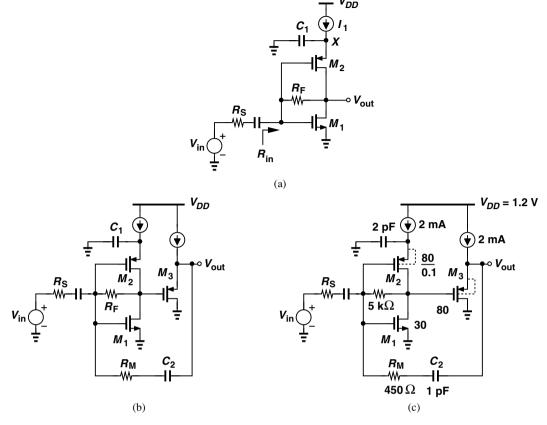

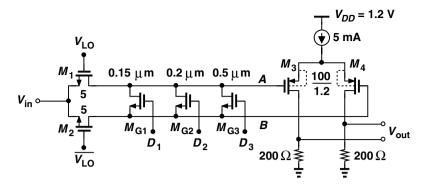

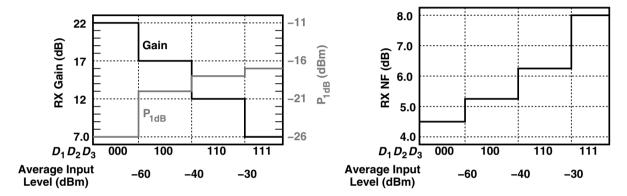

| 13.2   | Receiv   | er Design                  | 848 |

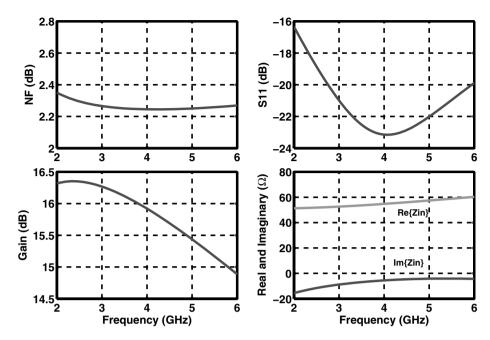

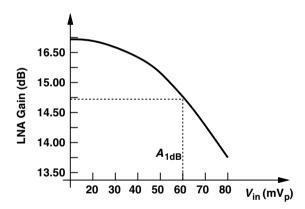

|        | 13.2.1   | LNA Design                 | 849 |

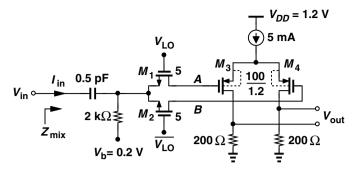

|        | 13.2.2   | Mixer Design               | 851 |

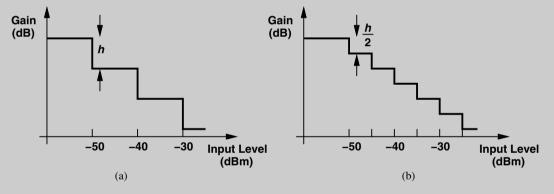

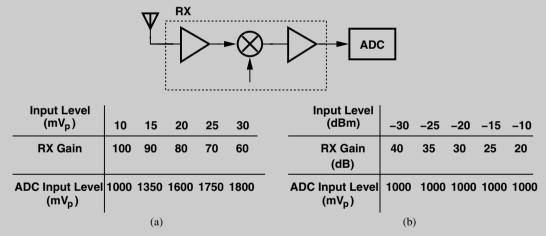

|        | 13.2.3   | AGC                        | 856 |

| 13.3   | TX De    | sign                       | 861 |

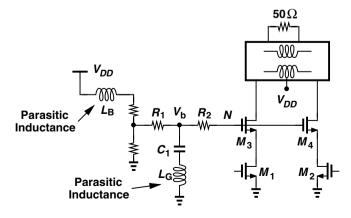

|        | 13.3.1   | PA Design                  | 861 |

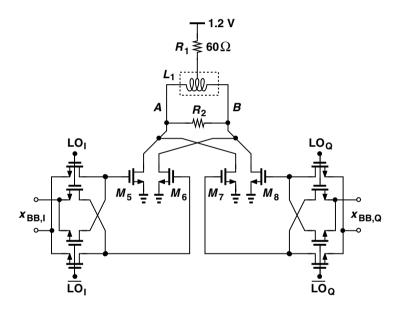

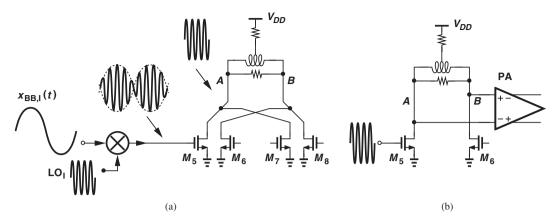

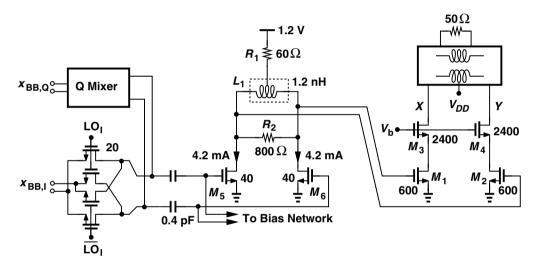

|        | 13.3.2   | Upconverter                | 867 |

| 13.4   | Synthe   | sizer Design               | 869 |

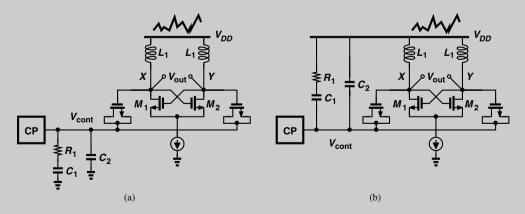

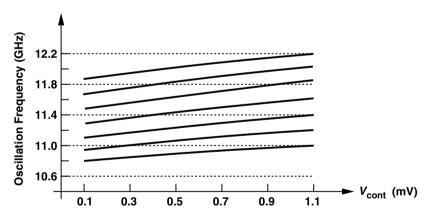

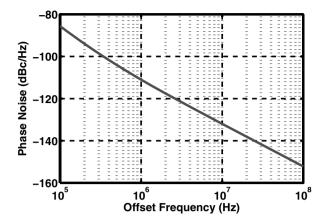

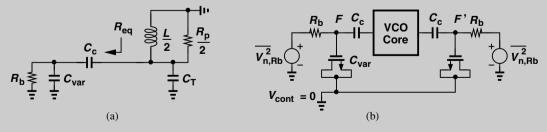

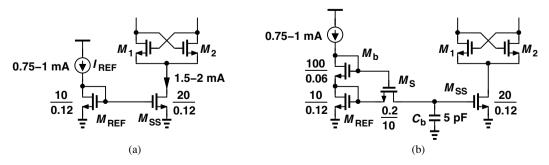

|        | 13.4.1   | VCO Design                 | 869 |

|        | 13.4.2   | Divider Design             | 878 |

|        | 13.4.3   | Loop Design                | 882 |

| Refe   | rences   |                            | 886 |

| Prob   | lems     |                            | 886 |

| INDEX  |          |                            | 889 |

|        |          |                            |     |

### PREFACE TO THE SECOND EDITION

In the 14 years since the first edition of this book, RF IC design has experienced a dramatic metamorphosis. Innovations in transceiver architectures, circuit topologies, and device structures have led to highly-integrated "radios" that span a broad spectrum of applications. Moreover, new analytical and modeling techniques have considerably improved our understanding of RF circuits and their underlying principles. A new edition was therefore due.

The second edition differs from the first in several respects:

- 1. I realized at the outset—three-and-a-half years ago—that simply adding "patches" to the first edition would not reflect today's RF microelectronics. I thus closed the first edition and began with a clean slate. The two editions have about 10% overlap.

- I wanted the second edition to contain greater pedagogy, helping the reader understand both the fundamentals and the subtleties. I have thus incorporated hundreds of examples and problems.

- 3. I also wanted to teach *design* in addition to analysis. I have thus included step-by-step design procedures and examples. Furthermore, I have dedicated Chapter 13 to the step-by-step transistor-level design of a dual-band WiFi transceiver.

- 4. With the tremendous advances in RF design, some of the chapters have inevitably become longer and some have been split into two or more chapters. As a result, the second edition is nearly three times as long as the first.

### **Suggestions for Instructors and Students**

The material in this book is much more than can be covered in one quarter or semester. The following is a possible sequence of the chapters that can be taught in one term with reasonable depth. Depending on the students' background and the instructor's preference, other combinations of topics can also be covered in one quarter or semester.

### **Chapter 1: Introduction to RF and Wireless Technology**

This chapter provides the big picture and should be covered in about half an hour.

### **Chapter 2: Basic Concepts in RF Design**

The following sections should be covered: General Considerations, Effects of Nonlinearity (the section on AM/PM Conversion can be skipped), Noise, and Sensitivity and Dynamic Range. (The sections on Passive Impedance Transformation, Scattering Parameters, and Analysis of Nonlinear Dynamic Systems can be skipped.) This chapter takes about six hours of lecture.

### **Chapter 3: Communication Concepts**

This chapter can be covered minimally in a quarter system—for example, Analog Modulation, Quadrature Modulation, GMSK Modulation, Multiple Access Techniques, and the IEEE802.11a/b/g Standard. In a semester system, the concept of signal constellations can be introduced and a few more modulation schemes and wireless standards can be taught. This chapter takes about two hours in a quarter system and three hours in a semester system.

### **Chapter 4: Transceiver Architectures**

This chapter is relatively long and should be taught selectively. The following sections should be covered: General Considerations, Basic and Modern Heterodyne Receivers, Direct-Conversion Receivers, Image-Reject Receivers, and Direct-Conversion Transmitters. In a semester system, Low-IF Receivers and Heterodyne Transmitters can be covered as well. This chapter takes about eight hours in a quarter system and ten hours in a semester system.

### **Chapter 5: Low-Noise Amplifiers**

The following sections should be covered: General Considerations, Problem of Input Matching, and LNA Topologies. A semester system can also include Gain Switching and Band Switching or High-IP<sub>2</sub> LNAs. This chapter takes about six hours in a quarter system and eight hours in a semester system.

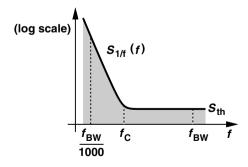

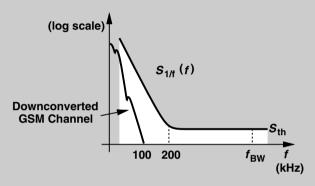

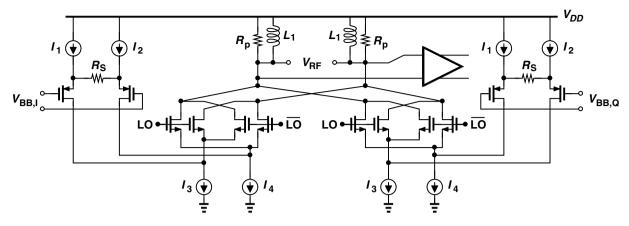

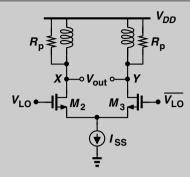

### **Chapter 6: Mixers**

The following sections should be covered: General Considerations, Passive Downconversion Mixers (the computation of noise and input impedance of voltage-driven sampling mixers can be skipped), Active Downconversion Mixers, and Active Mixers with High IP<sub>2</sub>. In a semester system, Active Mixers with Enhanced Transconductance, Active Mixers with Low Flicker Noise, and Upconversion Mixers can also be covered. This chapter takes about eight hours in a quarter system and ten hours in a semester system.

#### **Chapter 7: Passive Devices**

This chapter may not fit in a quarter system. In a semester system, about three hours can be spent on basic inductor structures and loss mechanisms and MOS varactors.

### **Chapter 8: Oscillators**

This is a long chapter and should be taught selectively. The following sections should be covered: Basic Principles, Cross-Coupled Oscillator, Voltage-Controlled

Oscillators, Low-Noise VCOs. In a quarter system, there is little time to cover phase noise. In a semester system, both approaches to phase noise analysis can be taught. This chapter takes about six hours in a quarter system and eight hours in a semester system.

### **Chapter 9: Phase-Locked Loops**

This chapter forms the foundation for synthesizers. In fact, if taught carefully, this chapter naturally teaches integer-N synthesizers, allowing a quarter system to skip the next chapter. The following sections should be covered: Basic Concepts, Type-I PLLs, Type-II PLLs, and PFD/CP Nonidealities. A semester system can also include Phase Noise in PLLs and Design Procedure. This chapter takes about four hours in a quarter system and six hours in a semester system.

### **Chapter 10: Integer-N Synthesizers**

This chapter is likely sacrificed in a quarter system. A semester system can spend about four hours on Spur Reduction Techniques and Divider Design.

### **Chapter 11: Fractional-N Synthesizers**

This chapter is likely sacrificed in a quarter system. A semester system can spend about four hours on Randomization and Noise Shaping. The remaining sections may be skipped.

### **Chapter 12: Power Amplifiers**

This is a long chapter and, unfortunately, is often sacrificed for other chapters. If coverage is desired, the following sections may be taught: General Considerations, Classification of Power Amplifiers, High-Efficiency Power Amplifiers, Cascode Output Stages, and Basic Linearization Techniques. These topics take about four hours of lecture. Another four hours can be spent on Doherty Power Amplifier, Polar Modulation, and Outphasing.

#### **Chapter 13: Transceiver Design Example**

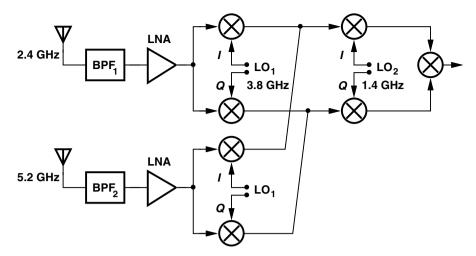

This chapter provides a step-by-step design of a dual-band transceiver. It is possible to skip the state-of-the-art examples in Chapters 5, 6, and 8 to allow some time for this chapter. The system-level derivations may still need to be skipped. The RX, TX, and synthesizer transistor-level designs can be covered in about four hours.

A solutions manual is available for instructors via the Pearson Higher Education Instructor Resource Center web site: pearsonhighered.com/irc; and a set of Powerpoint slides is available for instructors at **informit.com/razavi**. Additional problems will be posted on the book's website (**informit.com/razavi**).

—Behzad Razavi July 2011

### PREFACE TO THE FIRST EDITION

The annual worldwide sales of cellular phones has exceeded \$2.5B. With 4.5 million customers, home satellite networks comprise a \$2.5B industry. The global positioning system is expected to become a \$5B market by the year 2000. In Europe, the sales of equipment and services for mobile communications will reach \$30B by 1998. The statistics are overwhelming.

The radio frequency (RF) and wireless market has suddenly expanded to unimaginable dimensions. Devices such as pagers, cellular and cordless phones, cable modems, and RF identification tags are rapidly penetrating all aspects of our lives, evolving from luxury items to indispensable tools. Semiconductor and system companies, small and large, analog and digital, have seen the statistics and are striving to capture their own market share by introducing various RF products.

RF design is unique in that it draws upon many disciplines unrelated to integrated circuits (ICs). The RF knowledge base has grown for almost a century, creating a seemingly endless body of literature for the novice.

This book deals with the analysis and design of RF integrated circuits and systems. Providing a systematic treatment of RF electronics in a tutorial language, the book begins with the necessary background knowledge from microwave and communication theory and leads the reader to the design of RF transceivers and circuits. The text emphasizes both architecture and circuit level issues with respect to monolithic implementation in VLSI technologies. The primary focus is on bipolar and CMOS design, but most of the concepts can be applied to other technologies as well. The reader is assumed to have a basic understanding of analog IC design and the theory of signals and systems.

The book consists of nine chapters. Chapter 1 gives a general introduction, posing questions and providing motivation for subsequent chapters. Chapter 2 describes basic concepts in RF and microwave design, emphasizing the effects of nonlinearity and noise.

Chapters 3 and 4 take the reader to the communication system level, giving an overview of modulation, detection, multiple access techniques, and wireless standards. While initially appearing to be unnecessary, this material is in fact essential to the concurrent design of RF circuits and systems.

Chapter 5 deals with transceiver architectures, presenting various receiver and transmitter topologies along with their merits and drawbacks. This chapter also includes a number of case studies that exemplify the approaches taken in actual RF products.

Chapters 6 through 9 address the design of RF building blocks: low-noise amplifiers and mixers, oscillators, frequency synthesizers, and power amplifiers, with particular attention to minimizing the number of off-chip components. An important goal of these chapters is to demonstrate how the system requirements define the parameters of the circuits and how the performance of each circuit impacts that of the overall transceiver.

I have taught approximately 80% of the material in this book in a 4-unit graduate course at UCLA. Chapters 3, 4, 8, and 9 had to be shortened in a ten-week quarter, but in a semester system they can be covered more thoroughly.

Much of my RF design knowledge comes from interactions with colleagues. Helen Kim, Ting-Ping Liu, and Dan Avidor of Bell Laboratories, and David Su and Andrew Gzegorek of Hewlett-Packard Laboratories have contributed to the material in this book in many ways. The text was also reviewed by a number of experts: Stefan Heinen (Siemens), Bart Jansen (Hewlett-Packard), Ting-Ping Liu (Bell Labs), John Long (University of Toronto), Tadao Nakagawa (NTT), Gitty Nasserbakht (Texas Instruments), Ted Rappaport (Virginia Tech), Tirdad Sowlati (Gennum), Trudy Stetzler (Bell Labs), David Su (Hewlett-Packard), and Rick Wesel (UCLA). In addition, a number of UCLA students, including Farbod Behbahani, Hooman Darabi, John Leete, and Jacob Rael, "test drove" various chapters and provided useful feedback. I am indebted to all of the above for their kind assistance.

I would also like to thank the staff at Prentice Hall, particularly Russ Hall, Maureen Diana, and Kerry Riordan for their support.

—Behzad Razavi July 1997

### **ACKNOWLEDGMENTS**

I have been fortunate to benefit from the support of numerous people during the writing, review, and production phases of this book. I would like to express my thanks here.

Even after several rounds of self-editing, it is possible that typos or subtle mistakes have eluded the author. Sometimes, an explanation that is clear to the author may not be so to the reader. And, occasionally, the author may have missed a point or a recent development. A detailed review of the book by others thus becomes necessary. The following individuals meticulously reviewed various chapters, discovered my mistakes, and made valuable suggestions:

Ali Afsahi (Broadcom)

Pietro Andreani (Lund University) Ashkan Borna (UC Berkeley) Jonathan Borremans (IMEC)

Debopriyo Chowdhury (UC Berkeley)

Matteo Conta (Consultant) Ali Homayoun (UCLA)

Velntina del Lattorre (Consultant) Jane Gu (University of Florida)

Peng Han (Beken)

Pavan Hanumolu (Oregon State University) Rui Martins (University of Macau)

Daquan Huang (Texas Instruments)

Sy-Chyuan Hwu (UCLA) Amin Jahanian (UCI) Jithin Janardhan (UCLA) Shinwon Kang (UC Berkeley)

Iman Khajenasiri

(Sharif University of Technology)

Yanghyo Kim (UCLA)

Abbas Komijani (Atheros)

Tai-Cheng Lee (National Taiwan University) Antonio Liscidini (University of Pavia) Shen-Iuan Liu (National Taiwan University)

Xiaodong Liu (Lund University)

Jian Hua Lu (UCLA)

Howard Luong (Hong Kong University of

Science and Technology)

Elvis Mak (University of Macau)

Rabih Makarem (Atheros)

Andrea Mazzanti (University of Pavia)

Karthik Natarajan

(University of Washington)

Nitin Nidhi (UCLA) Joung Park (UCLA) Paul Park (Atheros) Stefano Pellerano (Intel) Jafar Savoj (Xilinx)

*Acknowledgments*

Parmoon Seddighrad Vidojkovic Vojkan (IMEC)

(University of Washington) Ning Wang (UCLA)

Alireza Shirvani (Ralink) Weifeng Wang (Beken)

Tirdad Sowlati (Qualcomm) Zhi Gong Wang (Southeast University)

Francesco Svelto (University of Pavia) Marco Zanuso (UCLA) Enrico Temporiti (ST Microelectronics) Yunfeng Zhao (Beken)

Federico Vecchi (University of Pavia) Alireza Zolfaghari (Broadcom)

Vijay Viswam (Lund University)

I am thankful for their enthusiastic, organized, and to-the-point reviews.

The book's production was proficiently managed by the staff at Prentice Hall, including Bernard Goodwin and Julie Nahil. I would like to thank both.

As with my other books, my wife, Angelina, typed the entire second edition in Latex and selflessly helped me in this three-and-a-half-year endeavor. I am grateful to her.

—Behzad Razavi

### ABOUT THE AUTHOR

**Behzad Razavi** received the BSEE degree from Sharif University of Technology in 1985 and MSEE and PhDEE degrees from Stanford University in 1988 and 1992, respectively. He was with AT&T Bell Laboratories and Hewlett-Packard Laboratories until 1996. Since 1996, he has been associate professor and, subsequently, professor of electrical engineering at University of California, Los Angeles. His current research includes wireless transceivers, frequency synthesizers, phase-locking and clock recovery for high-speed data communications, and data converters.

Professor Razavi was an adjunct professor at Princeton University from 1992 to 1994, and at Stanford University in 1995. He served on the Technical Program Committees of the International Solid-State Circuits Conference (ISSCC) from 1993 to 2002 and VLSI Circuits Symposium from 1998 to 2002. He has also served as guest editor and associate editor of the *IEEE Journal of Solid-State Circuits, IEEE Transactions on Circuits and Systems*, and *International Journal of High Speed Electronics*.

Professor Razavi received the Beatrice Winner Award for Editorial Excellence at the 1994 ISSCC; the best paper award at the 1994 European Solid-State Circuits Conference; the best panel award at the 1995 and 1997 ISSCC; the TRW Innovative Teaching Award in 1997; the best paper award at the IEEE Custom Integrated Circuits Conference (CICC) in 1998; and McGraw-Hill First Edition of the Year Award in 2001. He was the co-recipient of both the Jack Kilby Outstanding Student Paper Award and the Beatrice Winner Award for Editorial Excellence at the 2001 ISSCC. He received the Lockheed Martin Excellence in Teaching Award in 2006; the UCLA Faculty Senate Teaching Award in 2007; and the CICC Best Invited Paper Award in 2009. He was also recognized as one of the top ten authors in the fifty-year history of ISSCC. He received the IEEE Donald Pederson Award in Solid-State Circuits in 2012.

Professor Razavi is an IEEE Distinguished Lecturer, a Fellow of IEEE, and the author of *Principles of Data Conversion System Design*, *RF Microelectronics*, *First Edition* (translated to Chinese, Japanese, and Korean), *Design of Analog CMOS Integrated Circuits* (translated to Chinese, Japanese, and Korean), *Design of Integrated Circuits for*

XXIV About the Author

Optical Communications, and Fundamentals of Microelectronics (translated to Korean and Portuguese), and the editor of Monolithic Phase-Locked Loops and Clock Recovery Circuits and Phase-Locking in High-Performance Systems.

### **CHAPTER**

1

# INTRODUCTION TO RF AND WIRELESS TECHNOLOGY

Compare two RF transceivers designed for cell phones:

"A 2.7-V GSM RF Transceiver IC" [1] (published in 1997)

"A Single-Chip 10-Band WCDMA/HSDPA 4-Band GSM/EDGE SAW-Less CMOS Receiver with DigRF 3G Interface and +90-dBm IIP<sub>2</sub>" [2] (published in 2009)

Why is the latter much more complex than the former? Does the latter have a higher performance or only greater functionality? Which one costs more? Which one consumes a higher power? What do all the acronyms GSM, WCDMA, HSDPA, EDGE, SAW, and IIP<sub>2</sub> mean? Why do we care?

The field of RF communication has grown rapidly over the past two decades, reaching far into our lives and livelihood. Our cell phones serve as an encyclopedia, a shopping terminus, a GPS guide, a weather monitor, and a telephone—all thanks to their wireless communication devices. We can now measure a patient's brain or heart activity and transmit the results wirelessly, allowing the patient to move around untethered. We use RF devices to track merchandise, pets, cattle, children, and convicts.

### 1.1 A WIRELESS WORLD

Wireless communication has become almost as ubiquitous as electricity; our refrigerators and ovens may not have a wireless device at this time, but it is envisioned that our homes will eventually incorporate a wireless network that controls every device and appliance. High-speed wireless links will allow seamless connections among our laptops, digital cameras, camcorders, cell phones, printers, TVs, microwave ovens, etc. Today's WiFi and Bluetooth connections are simple examples of such links.

How did wireless communication take over the world? A confluence of factors has contributed to this explosive growth. The principal reason for the popularity of wireless

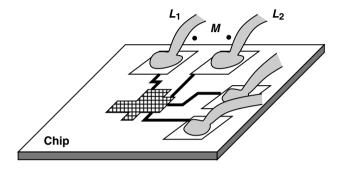

communication is the ever-decreasing cost of electronics. Today's cell phones cost about the same as those a decade ago but they offer many more functions and features: many frequency bands and communication modes, WiFi, Bluetooth, GPS, computing, storage, a digital camera, and a user-friendly interface. This affordability finds its roots in *integration*, i.e., how much functionality can be placed on a single chip—or, rather, how few components are left off-chip. The integration, in turn, owes its steady rise to (1) the scaling of VLSI processes, particularly, CMOS technology, and (2) innovations in RF architectures, circuits, and devices.

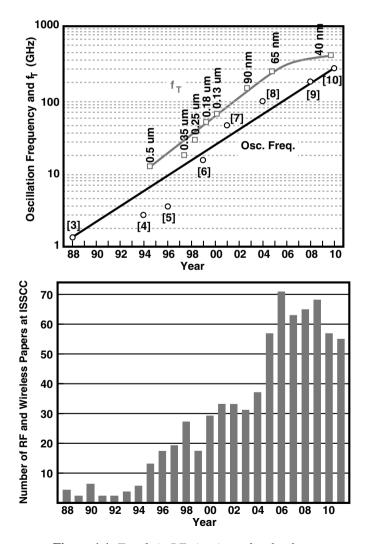

Along with higher integration levels, the performance of RF circuits has also improved. For example, the power consumption necessary for a given function has decreased and the speed of RF circuits has increased. Figure 1.1 illustrates some of the trends in RF integrated circuits (ICs) and technology for the past two decades. The minimum feature size of CMOS

**Figure 1.1** *Trends in RF circuits and technology.*

technology has fallen from 0.5  $\mu$ m to 40 nm, the transit frequency,  $f_T$ , of NMOS devices has risen from about 12 GHz to several hundred gigahertz, and the speed of RF oscillators has gone from 1.2 GHz to 300 GHz. Also shown is the number of RF and wireless design papers presented at the International Solid-State Circuits Conference (ISSCC) each year, revealing the fast-growing activity in this field.

### 1.2 RF DESIGN IS CHALLENGING

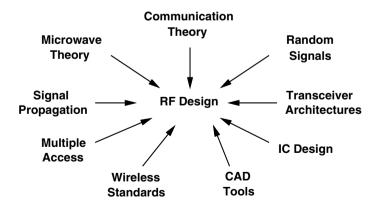

Despite many decades of work on RF and microwave theory and two decades of research on RF ICs, the design and implementation of RF circuits and transceivers remain challenging. This is for three reasons. First, as shown in Fig. 1.2, RF design draws upon a multitude of disciplines, requiring a good understanding of fields that are seemingly irrelevant to integrated circuits. Most of these fields have been under study for more than half a century, presenting a massive body of knowledge to a person entering RF IC design. One objective of this book is to provide the necessary background from these disciplines without overwhelming the reader.

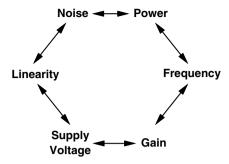

Second, RF circuits and transceivers must deal with numerous trade-offs, summarized in the "RF design hexagon" of Fig. 1.3. For example, to lower the noise of a front-end amplifier, we must consume a greater power or sacrifice linearity. We will encounter these trade-offs throughout this book.

Third, the demand for higher performance, lower cost, and greater functionality continues to present new challenges. The early RF IC design work in the 1990s strove to integrate *one* transceiver—perhaps along with the digital baseband processor—on a single chip. Today's efforts, on the other hand, aim to accommodate multiple transceivers operating in different frequency bands for different wireless standards (e.g., Bluetooth, WiFi, GPS, etc.). The two papers mentioned at the beginning of this chapter exemplify this trend. It is interesting to note that the silicon chip area of early single-transceiver systems was

**Figure 1.2** *Various disciplines necessary in RF design.*

<sup>1.</sup> The transit frequency is defined as the frequency at which the small-signal current gain of a device falls to unity.

**Figure 1.3** *RF design hexagon.*

dominated by the digital baseband processor, allowing RF and analog designers some latitude in the choice of their circuit and device topologies. In today's designs, however, the multiple transceivers tend to occupy a *larger* area than the baseband processor, requiring that RF and analog sections be designed with much care about their area consumption. For example, while on-chip spiral inductors (which have a large footprint) were utilized in abundance in older systems, they are now used only sparingly.

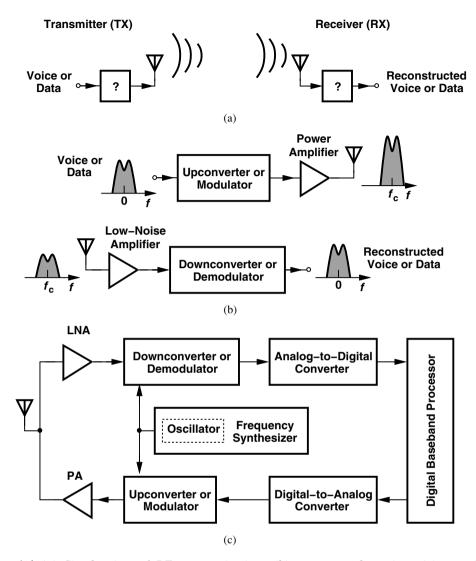

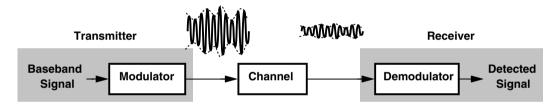

### 1.3 THE BIG PICTURE

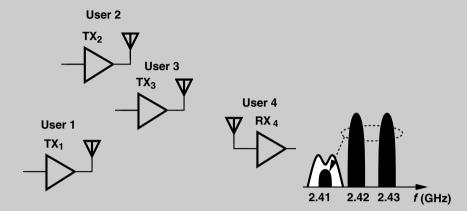

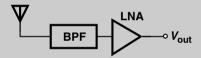

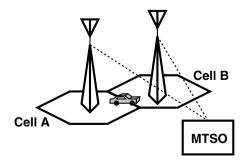

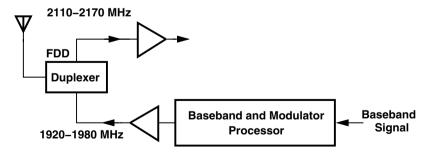

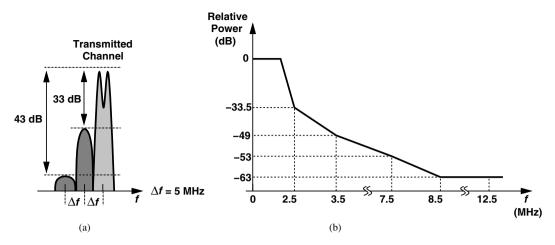

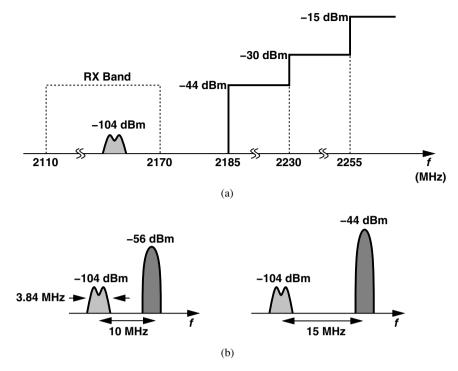

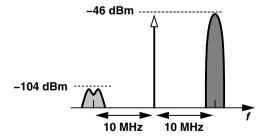

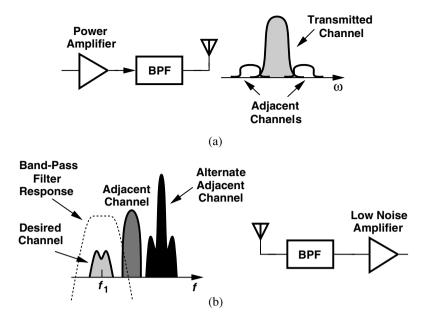

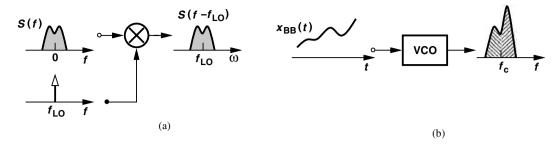

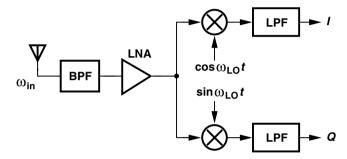

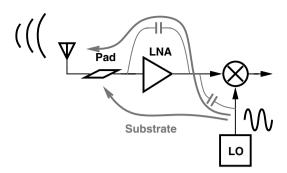

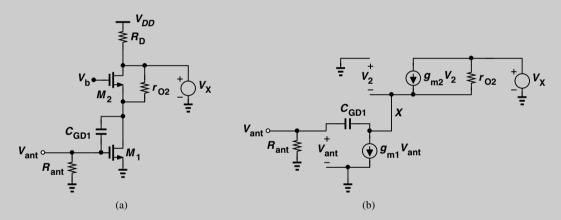

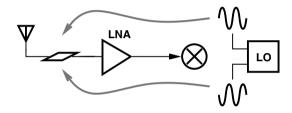

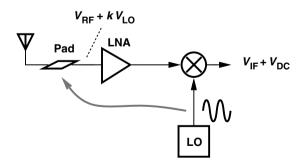

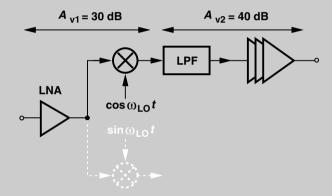

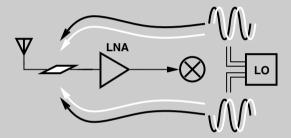

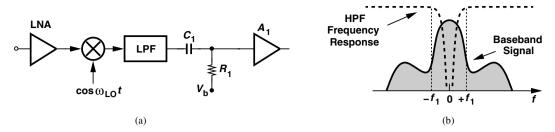

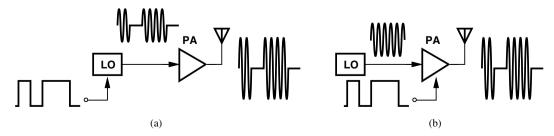

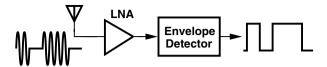

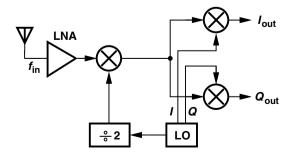

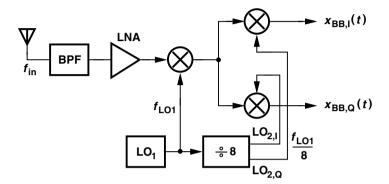

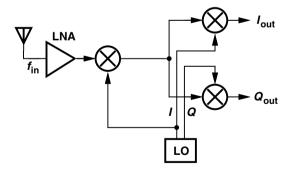

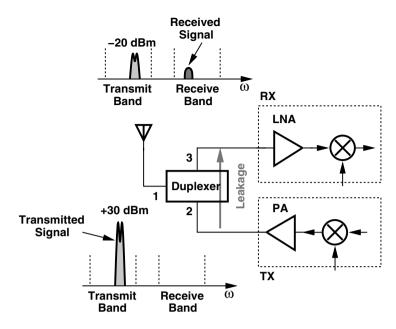

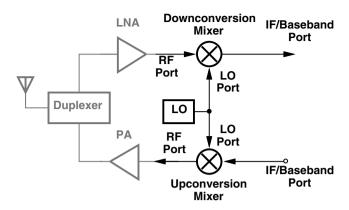

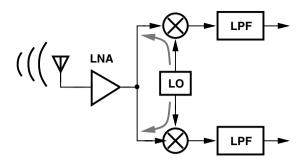

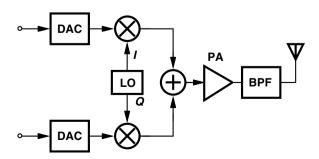

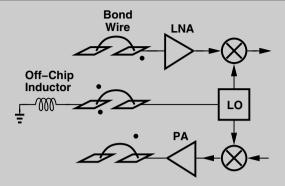

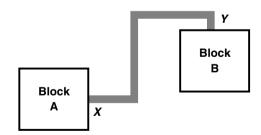

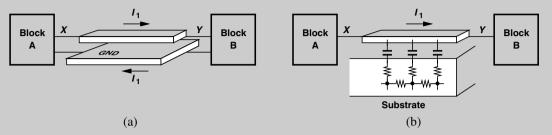

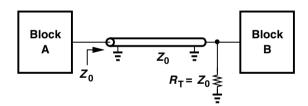

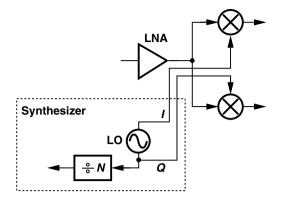

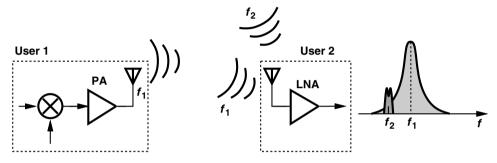

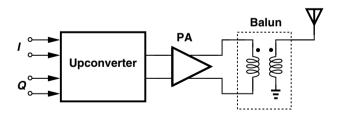

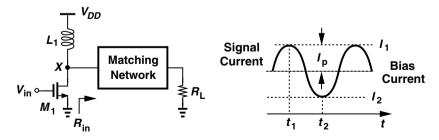

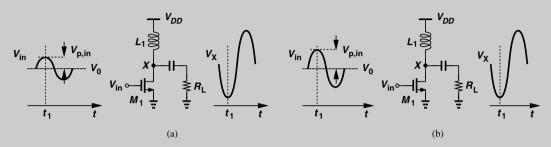

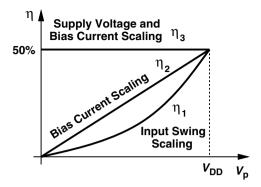

The objective of an RF transceiver is to transmit and receive information. We envision that the transmitter (TX) somehow processes the voice or data signal and applies the result to the antenna [Fig. 1.4(a)]. Similarly, the receiver (RX) senses the signal picked up by the antenna and processes it so as to reconstruct the original voice or data information. Each black box in Fig. 1.4(a) contains a great many functions, but we can readily make two observations: (1) the TX must drive the antenna with a high power level so that the transmitted signal is strong enough to reach far distances, and (2) the RX may sense a small signal (e.g., when a cell phone is used in the basement of a building) and must first amplify the signal with low noise. We now architect our transceiver as shown in Fig. 1.4(b), where the signal to be transmitted is first applied to a "modulator" or "upconverter" so that its center frequency goes from zero to, say,  $f_c = 2.4$  GHz. The result drives the antenna through a "power amplifier" (PA). On the receiver side, the signal is sensed by a "lownoise amplifier" (LNA) and subsequently by a "downconverter" or "demodulator" (also known as a "detector").

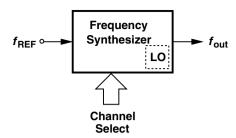

The upconversion and downconversion paths in Fig. 1.4(b) are driven by an oscillator, which itself is controlled by a "frequency synthesizer." Figure 1.4(c) shows the overall transceiver.<sup>2</sup> The system looks deceptively simple, but we will need the next 900 pages to cover its RF sections. And perhaps another 900 pages to cover the analog-to-digital and digital-to-analog converters.

<sup>2.</sup> In some cases, the modulator and the upconverter are one and the same. In some other cases, the modulation is performed in the digital domain before upconversion. Most receivers demodulate and detect the signal digitally, requiring only a downconverter in the analog domain.

*References* 5

**Figure 1.4** (a) Simple view of RF communication, (b) more complete view, (c) generic RF transceiver.

### REFERENCES

- [1] T. Yamawaki et al., "A 2.7-V GSM RF Transceiver IC," *IEEE J. Solid-State Circuits*, vol. 32, pp. 2089–2096, Dec. 1997.

- [2] D. Kaczman et al., "A Single-Chip 10-Band WCDMA/HSDPA 4-Band GSM/EDGE SAWless CMOS Receiver with DigRF 3G Interface and +90-dBm IIP2," *IEEE J. Solid-State Circuits*, vol. 44, pp. 718–739, March 2009.

- [3] M. Banu, "MOS Oscillators with Multi-Decade Tuning Range and Gigahertz Maximum Speed," *IEEE J. Solid-State Circuits*, vol. 23, pp. 474–479, April 1988.

- [4] B. Razavi et al., "A 3-GHz 25-mW CMOS Phase-Locked Loop," *Dig. of Symposium on VLSI Circuits*, pp. 131–132, June 1994.

- [5] M. Soyuer et al., "A 3-V 4-GHz nMOS Voltage-Controlled Oscillator with Integrated Resonator," *IEEE J. Solid-State Circuits*, vol. 31, pp. 2042–2045, Dec. 1996.

- [6] B. Kleveland et al., "Monolithic CMOS Distributed Amplifier and Oscillator," *ISSCC Dig. Tech. Papers*, pp. 70–71, Feb. 1999.

- [7] H. Wang, "A 50-GHz VCO in 0.25-μm CMOS," *ISSCC Dig. Tech. Papers*, pp. 372–373, Feb. 2001.

- [8] L. Franca-Neto, R. Bishop, and B. Bloechel, "64 GHz and 100 GHz VCOs in 90 nm CMOS Using Optimum Pumping Method," ISSCC Dig. Tech. Papers, pp. 444–445, Feb. 2004.

- [9] E. Seok et al., "A 410GHz CMOS Push-Push Oscillator with an On-Chip Patch Antenna" *ISSCC Dig. Tech. Papers*, pp. 472–473, Feb. 2008.

- [10] B. Razavi, "A 300-GHz Fundamental Oscillator in 65-nm CMOS Technology," *Symposium on VLSI Circuits Dig. Of Tech. Papers*, pp. 113–114, June 2010.

**CHAPTER**

### **BASIC CONCEPTS IN RF DESIGN**

RF design draws upon many concepts from a variety of fields, including signals and systems, electromagnetics and microwave theory, and communications. Nonetheless, RF design has developed its own analytical methods and its own language. For example, while the nonlinear behavior of analog circuits may be characterized by "harmonic distortion," that of RF circuits is quantified by very different measures.

This chapter deals with general concepts that prove essential to the analysis and design of RF circuits, closing the gaps with respect to other fields such as analog design, microwave theory, and communication systems. The outline is shown below.

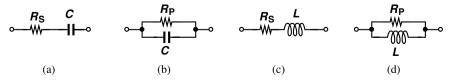

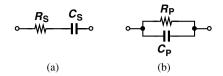

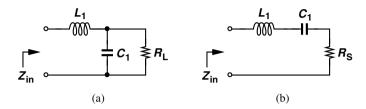

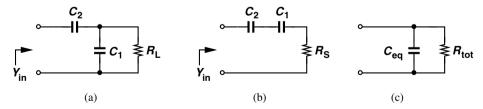

| Nonlinearity              | Noise             | Impedance Transformation     |  |

|---------------------------|-------------------|------------------------------|--|

| ■ Harmonic Distortion     | ■ Noise Spectrum  | ■ Series-Parallel Conversion |  |

| Compression               | Device Noise      | Matching Networks            |  |

| Intermodulation           | Noise in Circuits | S-Parameters                 |  |

| Dynamic Nonlinear Systems |                   |                              |  |

#### 2.1 GENERAL CONSIDERATIONS

#### 2.1.1 Units in RF Design

RF design has traditionally employed certain units to express gains and signal levels. It is helpful to review these units at the outset so that we can comfortably use them in our subsequent studies.

The voltage gain,  $V_{out}/V_{in}$ , and power gain,  $P_{out}/P_{in}$ , are expressed in decibels (dB):

$$A_{V|dB} = 20 \log \frac{V_{out}}{V_{in}}$$

$$A_{P|dB} = 10 \log \frac{P_{out}}{P_{in}}.$$

(2.1)

$$A_P|_{\rm dB} = 10\log\frac{P_{out}}{P_{i...}}.$$

(2.2)

These two quantities are equal (in dB) only if the input and output voltages appear across equal impedances. For example, an amplifier having an input resistance of  $R_0$  (e.g., 50  $\Omega$ ) and driving a load resistance of  $R_0$  satisfies the following equation:

$$A_P|_{\rm dB} = 10 \log \frac{\frac{V_{out}^2}{R_0}}{\frac{V_{in}^2}{R_0}}$$

(2.3)

$$=20\log\frac{V_{out}}{V_{in}}\tag{2.4}$$

$$=A_V|_{\mathrm{dB}},\tag{2.5}$$

where  $V_{out}$  and  $V_{in}$  are rms values. In many RF systems, however, this relationship does not hold because the input and output impedances are not equal.

The absolute signal levels are often expressed in dBm rather than in watts or volts. Used for power quantities, the unit dBm refers to "dB's above 1 mW." To express the signal power,  $P_{Sig}$ , in dBm, we write

$$P_{sig}|_{\text{dBm}} = 10 \log \left( \frac{P_{sig}}{1 \text{ mW}} \right). \tag{2.6}$$

### Example 2.1

An amplifier senses a sinusoidal signal and delivers a power of  $0 \, dBm$  to a load resistance of  $50 \, \Omega$ . Determine the peak-to-peak voltage swing across the load.

### **Solution:**

Since 0 dBm is equivalent to 1 mW, for a sinusoidal having a peak-to-peak amplitude of  $V_{pp}$  and hence an rms value of  $V_{pp}/(2\sqrt{2})$ , we write

$$\frac{V_{pp}^2}{8R_L} = 1 \text{ mW}, (2.7)$$

where  $R_L = 50 \Omega$ . Thus,

$$V_{pp} = 632 \text{ mV}.$$

(2.8)

This is an extremely useful result, as demonstrated in the next example.

### Example 2.2

A GSM receiver senses a narrowband (modulated) signal having a level of  $-100 \, \text{dBm}$ . If the front-end amplifier provides a voltage gain of 15 dB, calculate the peak-to-peak voltage swing at the output of the amplifier.

### **Example 2.2** (Continued)

#### Solution:

Since the amplifier output *voltage* swing is of interest, we first convert the received signal level to voltage. From the previous example, we note that  $-100\,\mathrm{dBm}$  is  $100\,\mathrm{dB}$  below  $632\,\mathrm{mV_{pp}}$ . Also,  $100\,\mathrm{dB}$  for voltage quantities is equivalent to  $10^5$ . Thus,  $-100\,\mathrm{dBm}$  is equivalent to  $6.32\,\mu\mathrm{V_{pp}}$ . This input level is amplified by  $15\,\mathrm{dB}$  ( $\approx 5.62$ ), resulting in an output swing of  $35.5\,\mu\mathrm{V_{pp}}$ .

The reader may wonder why the output *voltage* of the amplifier is of interest in the above example. This may occur if the circuit following the amplifier does not present a  $50-\Omega$  input impedance, and hence the power gain and voltage gain are not equal in dB. In fact, the next stage may exhibit a purely *capacitive* input impedance, thereby requiring no signal "power." This situation is more familiar in analog circuits wherein one stage drives the gate of the transistor in the next stage. As explained in Chapter 5, in most integrated RF systems, we prefer voltage quantities to power quantities so as to avoid confusion if the input and output impedances of cascade stages are unequal or contain negligible real parts.

The reader may also wonder why we were able to assume  $0\,dBm$  is equivalent to  $632\,mV_{pp}$  in the above example even though the signal is not a pure sinusoid. After all, only for a sinusoid can we assume that the rms value is equal to the peak-to-peak value divided by  $2\sqrt{2}$ . Fortunately, for a narrowband 0-dBm signal, it is still possible to approximate the (average) peak-to-peak swing as  $632\,mV$ .

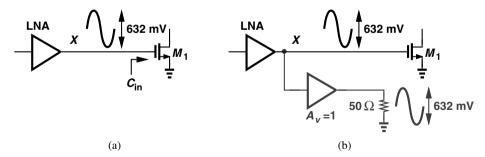

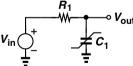

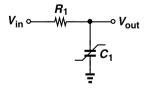

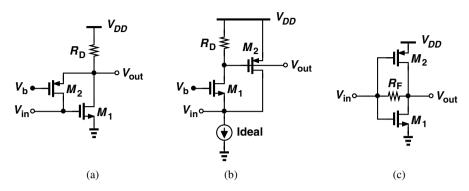

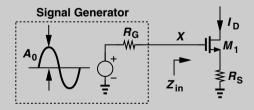

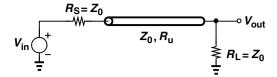

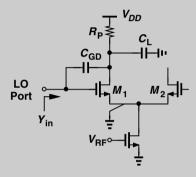

Although dBm is a unit of power, we sometimes use it at interfaces that do not necessarily entail power transfer. For example, consider the case shown in Fig. 2.1(a), where the LNA drives a purely-capacitive load with a 632-mV<sub>pp</sub> swing, delivering no average power. We mentally attach an ideal voltage buffer to node X and drive a 50- $\Omega$  load [Fig. 2.1(b)]. We then say that the signal at node X has a level of 0 dBm, tacitly meaning that *if* this signal were applied to a 50- $\Omega$  load, *then* it would deliver 1 mW.

**Figure 2.1** (a) LNA driving a capacitive impedance, (b) use of fictitious buffer to visualize the signal level in dBm.

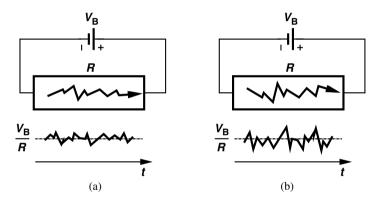

#### 2.1.2 Time Variance

A system is linear if its output can be expressed as a linear combination (superposition) of responses to individual inputs. More specifically, if the outputs in response to inputs  $x_1(t)$

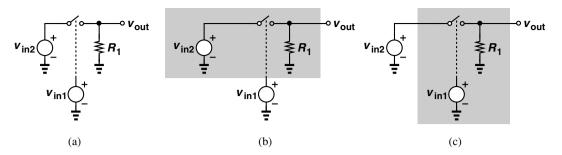

**Figure 2.2** (a) Simple switching circuit, (b) system with  $V_{in1}$  as the input, (c) system with  $V_{in2}$  as the input.

and  $x_2(t)$  can be respectively expressed as

$$y_1(t) = f[x_1(t)]$$

(2.9)

$$y_2(t) = f[x_2(t)],$$

(2.10)

then.

$$ay_1(t) + by_2(t) = f[ax_1(t) + bx_2(t)],$$

(2.11)

for arbitrary values of *a* and *b*. Any system that does not satisfy this condition is nonlinear. Note that, according to this definition, nonzero initial conditions or dc offsets also make a system nonlinear, but we often relax the rule to accommodate these two effects.

Another attribute of systems that may be confused with nonlinearity is time variance. A system is time-invariant if a time shift in its input results in the same time shift in its output. That is, if y(t) = f[x(t)], then  $y(t - \tau) = f[x(t - \tau)]$  for arbitrary  $\tau$ .

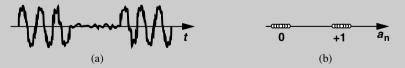

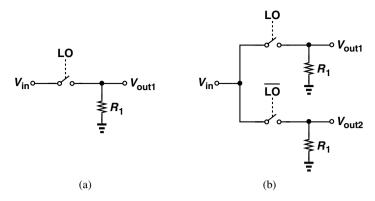

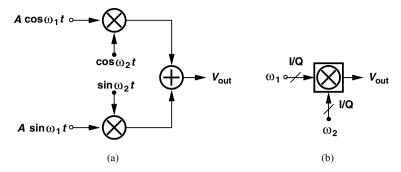

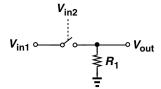

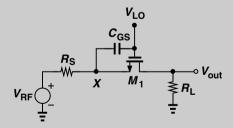

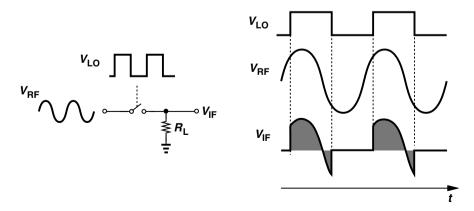

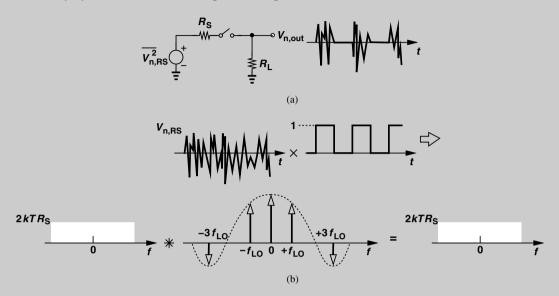

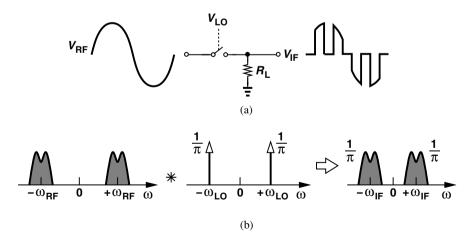

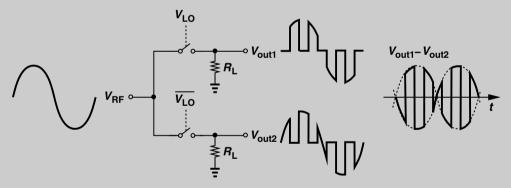

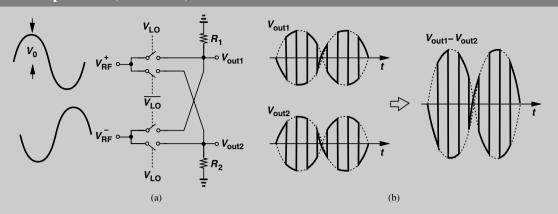

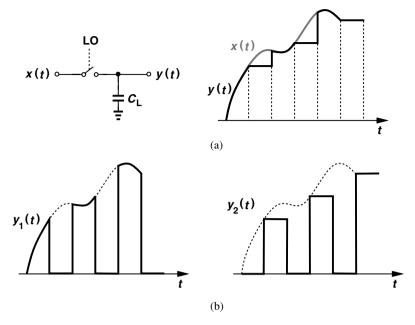

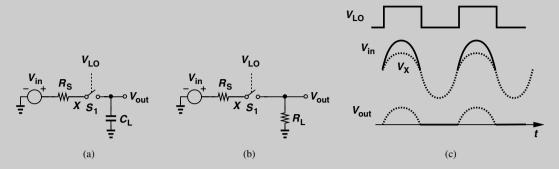

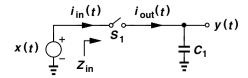

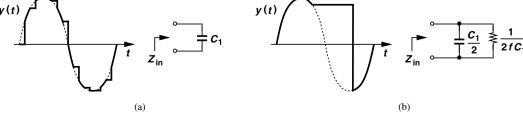

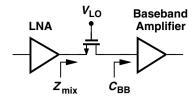

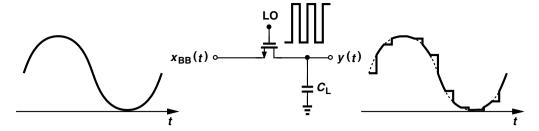

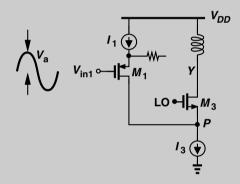

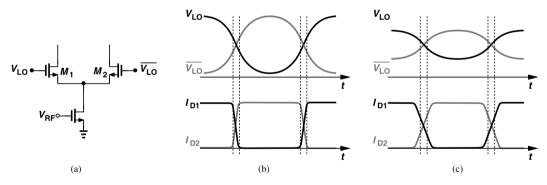

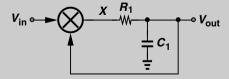

As an example of an RF circuit in which time variance plays a critical role and must not be confused with nonlinearity, let us consider the simple switching circuit shown in Fig. 2.2(a). The control terminal of the switch is driven by  $v_{in1}(t) = A_1 \cos \omega_1 t$  and the input terminal by  $v_{in2}(t) = A_2 \cos \omega_2 t$ . We assume the switch is on if  $v_{in1} > 0$  and off otherwise. Is this system nonlinear or time-variant? If, as depicted in Fig. 2.2(b), the input of interest is  $v_{in1}$  (while  $v_{in2}$  is part of the system and still equal to  $A_2 \cos \omega_2 t$ ), then the system is nonlinear because the control is only sensitive to the polarity of  $v_{in1}$  and independent of its amplitude. This system is also time-variant because the output depends on  $v_{in2}$ . For example, if  $v_{in1}$  is constant and positive, then  $v_{out}(t) = v_{in2}(t)$ , and if  $v_{in1}$  is constant and negative, then  $v_{out}(t) = 0$  (why?).

Now consider the case shown in Fig. 2.2(c), where the input of interest is  $v_{in2}$  (while  $v_{in1}$  remains part of the system and still equal to  $A_1 \cos \omega_1 t$ ). This system is linear with respect to  $v_{in2}$ . For example, doubling the amplitude of  $v_{in2}$  directly doubles that of  $v_{out}$ . The system is also time-variant due to the effect of  $v_{in1}$ .

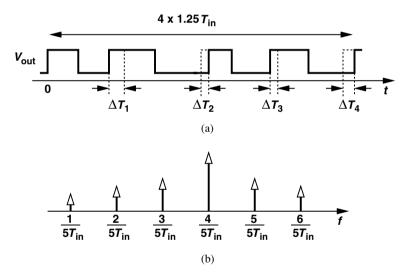

### Example 2.3

Plot the output waveform of the circuit in Fig. 2.2(a) if  $v_{in1} = A_1 \cos \omega_1 t$  and  $v_{in2} = A_2 \cos(1.25\omega_1 t)$ .

### **Example 2.3** (Continued)

#### **Solution:**

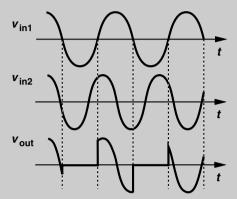

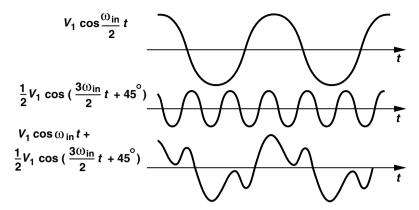

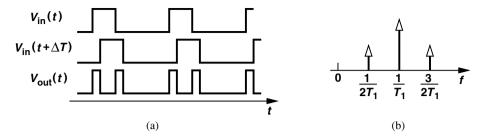

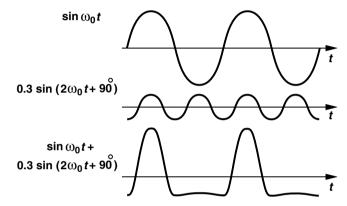

As shown in Fig. 2.3,  $v_{out}$  tracks  $v_{in2}$  if  $v_{in1} > 0$  and is pulled down to zero by  $R_1$  if  $v_{in1} < 0$ . That is,  $v_{out}$  is equal to the product of  $v_{in2}$  and a square wave toggling between 0 and 1.

Figure 2.3 Input and output waveforms.

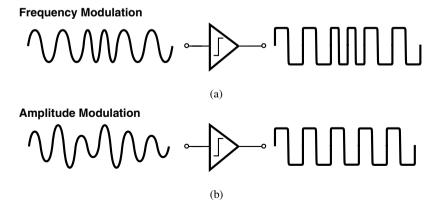

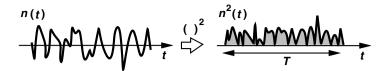

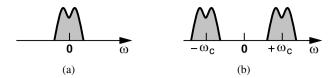

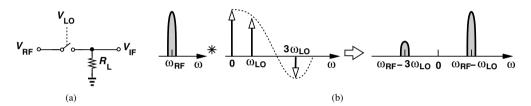

The circuit of Fig. 2.2(a) is an example of RF "mixers." We will study such circuits in Chapter 6 extensively, but it is important to draw several conclusions from the above study. First, statements such as "switches are nonlinear" are ambiguous. Second, a linear system *can* generate frequency components that do not exist in the input signal—the system only need be time-variant. From Example 2.3,

$$v_{out}(t) = v_{in2}(t) \cdot S(t), \tag{2.12}$$

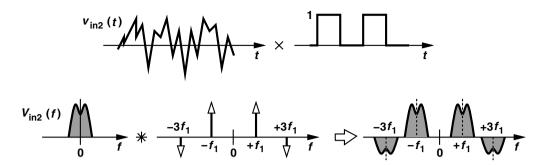

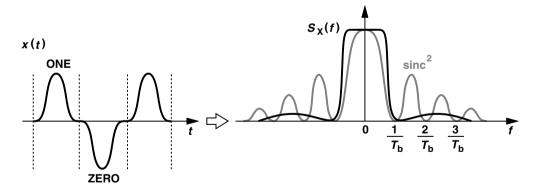

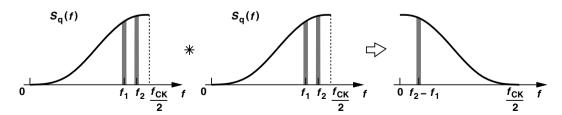

where S(t) denotes a square wave toggling between 0 and 1 with a frequency of  $f_1 = \omega_1/(2\pi)$ . The output spectrum is therefore given by the convolution of the spectra of  $v_{in2}(t)$  and S(t). Since the spectrum of a square wave is equal to a train of impulses whose amplitudes follow a sinc envelope, we have

$$V_{out}(f) = V_{in2}(f) * \sum_{n = -\infty}^{+\infty} \frac{\sin(n\pi/2)}{n\pi} \delta\left(f - \frac{n}{T_1}\right)$$

(2.13)

$$=\sum_{n=-\infty}^{+\infty} \frac{\sin(n\pi/2)}{n\pi} V_{in2} \left( f - \frac{n}{T_1} \right), \tag{2.14}$$

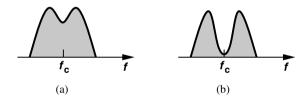

where  $T_1 = 2\pi/\omega_1$ . This operation is illustrated in Fig. 2.4 for a  $V_{in2}$  spectrum located around zero frequency.<sup>1</sup>

<sup>1.</sup> It is helpful to remember that, for n = 1, each impulse in the above summation has an area of  $1/\pi$  and the corresponding sinusoid, a *peak amplitude* of  $2/\pi$ .

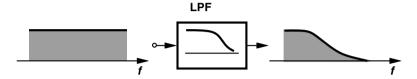

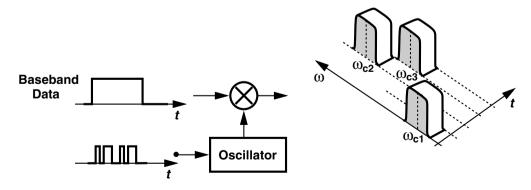

**Figure 2.4** Multiplication in the time domain and corresponding convolution in the frequency domain.

# 2.1.3 Nonlinearity

A system is called "memoryless" or "static" if its output does not depend on the past values of its input (or the past values of the output itself). For a memoryless linear system, the input/output characteristic is given by

$$y(t) = \alpha x(t), \tag{2.15}$$

where  $\alpha$  is a function of time if the system is time-variant [e.g., Fig. 2.2(c)]. For a memoryless nonlinear system, the input/output characteristic can be approximated with a polynomial,

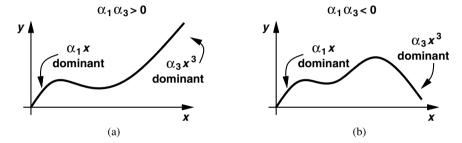

$$y(t) = \alpha_0 + \alpha_1 x(t) + \alpha_2 x^2(t) + \alpha_3 x^3(t) + \cdots, \tag{2.16}$$

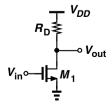

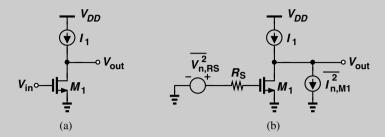

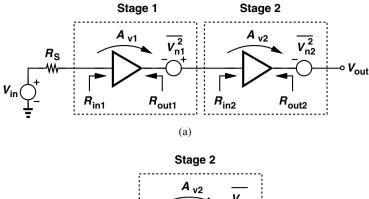

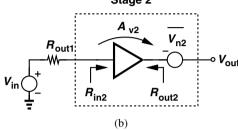

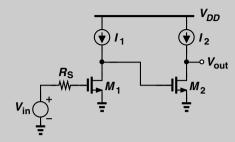

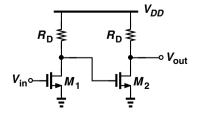

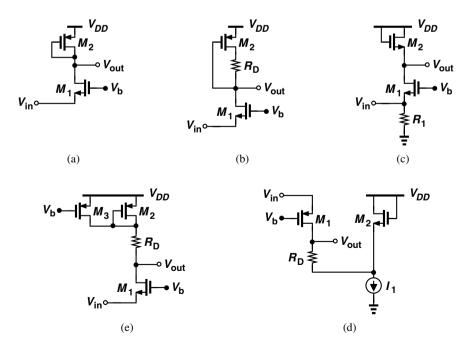

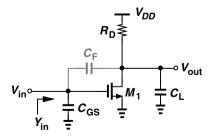

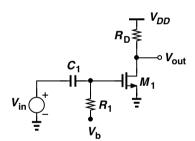

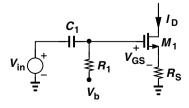

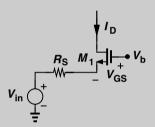

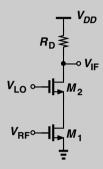

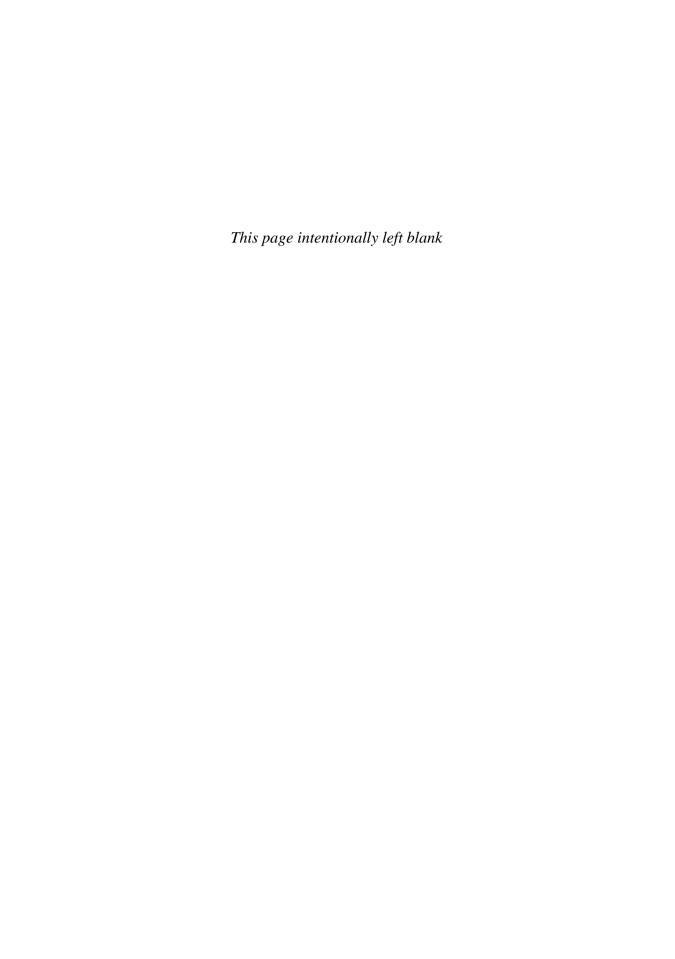

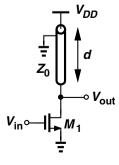

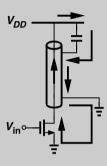

where  $\alpha_j$  may be functions of time if the system is time-variant. Figure 2.5 shows a common-source stage as an example of a memoryless nonlinear circuit (at low frequencies). If  $M_1$  operates in the saturation region and can be approximated as a square-law device, then

$$V_{out} = V_{DD} - I_D R_D (2.17)$$

$$= V_{DD} - \frac{1}{2}\mu_n C_{ox} \frac{W}{I} (V_{in} - V_{TH})^2 R_D.$$

(2.18)

In this idealized case, the circuit displays only second-order nonlinearity.

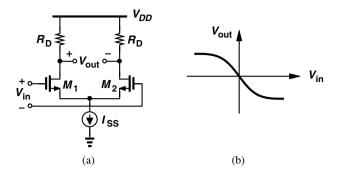

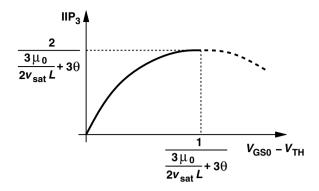

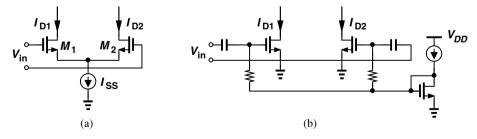

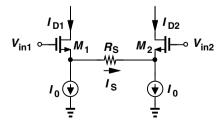

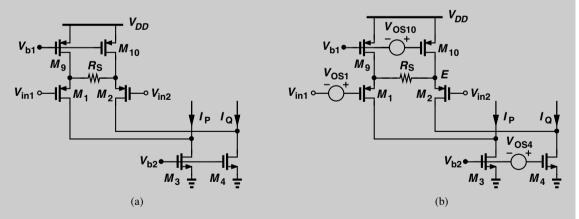

The system described by Eq. (2.16) has "odd symmetry" if y(t) is an odd function of x(t), i.e., if the response to -x(t) is the negative of that to +x(t). This occurs if  $\alpha_j = 0$  for even j. Such a system is sometimes called "balanced," as exemplified by the differential

Figure 2.5 Common-source stage.

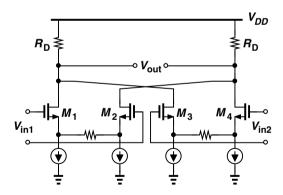

**Figure 2.6** (a) Differential pair and (b) its input/output characteristic.

pair shown in Fig. 2.6(a). Recall from basic analog design that by virtue of symmetry, the circuit exhibits the characteristic depicted in Fig. 2.6(b) if the differential input varies from very negative values to very positive values.

### Example 2.4

For square-law MOS transistors operating in saturation, the characteristic of Fig. 2.6(b) can be expressed as [1]

$$V_{out} = -\frac{1}{2}\mu_n C_{ox} \frac{W}{L} V_{in} \sqrt{\frac{4I_{SS}}{\mu_n C_{ox} \frac{W}{L}} - V_{in}^2} R_D.$$

(2.19)

If the differential input is small, approximate the characteristic by a polynomial.

#### **Solution:**

Factoring  $4I_{SS}/(\mu_n C_{ox}W/L)$  out of the square root and assuming

$$V_{in}^2 \ll \frac{4I_{SS}}{\mu_n C_{ox} \frac{W}{I}},\tag{2.20}$$

we use the approximation  $\sqrt{1-\epsilon} \approx 1 - \epsilon/2$  to write

$$V_{out} \approx -\sqrt{\mu_n C_{ox} \frac{W}{L} I_{SS}} V_{in} \left( 1 - \frac{\mu_n C_{ox} \frac{W}{L}}{8 I_{SS}} V_{in}^2 \right) R_D$$

(2.21)

$$\approx -\sqrt{\mu_n C_{ox} \frac{W}{L} I_{SS} R_D V_{in}} + \frac{\left(\mu_n C_{ox} \frac{W}{L}\right)^{3/2}}{8\sqrt{I_{SS}}} R_D V_{in}^3. \tag{2.22}$$

The first term on the right-hand side represents linear operation, revealing the small-signal voltage gain of the circuit  $(-g_m R_D)$ . Due to symmetry, even-order nonlinear terms are absent. Interestingly, square-law devices yield a *third-order* characteristic in this case. We return to this point in Chapter 5.

A system is called "dynamic" if its output depends on the past values of its input(s) or output(s). For a linear, time-invariant, dynamic system,

$$y(t) = h(t) * x(t),$$

(2.23)

where h(t) denotes the impulse response. If a dynamic system is linear but time-variant, its impulse response depends on the time origin; if  $\delta(t)$  yields h(t), then  $\delta(t-\tau)$  produces  $h(t,\tau)$ . Thus,

$$y(t) = h(t, \tau) * x(t).$$

(2.24)

Finally, if a system is both nonlinear and dynamic, then its impulse response can be approximated by a Volterra series. This is described in Section 2.8.

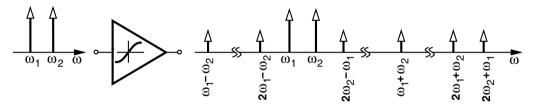

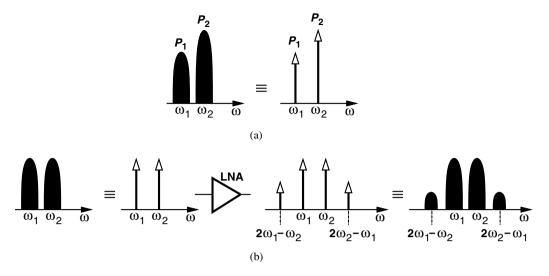

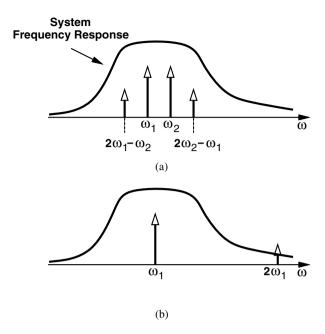

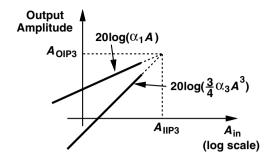

### 2.2 EFFECTS OF NONLINEARITY

While analog and RF circuits can be approximated by a linear model for small-signal operation, nonlinearities often lead to interesting and important phenomena that are not predicted by small-signal models. In this section, we study these phenomena for memoryless systems whose input/output characteristic can be approximated by<sup>2</sup>

$$y(t) \approx \alpha_1 x(t) + \alpha_2 x^2(t) + \alpha_3 x^3(t).$$

(2.25)

The reader is cautioned, however, that the effect of storage elements (dynamic nonlinearity) and higher-order nonlinear terms must be carefully examined to ensure (2.25) is a plausible representation. Section 2.7 deals with the case of dynamic nonlinearity. We may consider  $\alpha_1$  as the small-signal gain of the system because the other two terms are negligible for small input swings. For example,  $\alpha_1 = -\sqrt{\mu_n C_{ox}(W/L)I_{SS}R_D}$  in Eq. (2.22).

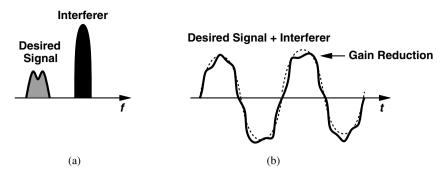

The nonlinearity effects described in this section primarily arise from the third-order term in Eq. (2.25). The second-order term too manifests itself in certain types of receivers and is studied in Chapter 4.

#### 2.2.1 Harmonic Distortion

If a sinusoid is applied to a nonlinear system, the output generally exhibits frequency components that are integer multiples ("harmonics") of the input frequency. In Eq. (2.25), if  $x(t) = A \cos \omega t$ , then

$$y(t) = \alpha_1 A \cos \omega t + \alpha_2 A^2 \cos^2 \omega t + \alpha_3 A^3 \cos^3 \omega t$$

(2.26)

$$= \alpha_1 A \cos \omega t + \frac{\alpha_2 A^2}{2} (1 + \cos 2\omega t) + \frac{\alpha_3 A^3}{4} (3 \cos \omega t + \cos 3\omega t)$$

(2.27)

$$= \frac{\alpha_2 A^2}{2} + \left(\alpha_1 A + \frac{3\alpha_3 A^3}{4}\right) \cos \omega t + \frac{\alpha_2 A^2}{2} \cos 2\omega t + \frac{\alpha_3 A^3}{4} \cos 3\omega t. \quad (2.28)$$

<sup>2.</sup> Note that this expression should be considered as a fit across the signal swings of interest rather than as a Taylor expansion in the vicinity of x = 0. These two views may yield slightly different values for  $\alpha_j$ .

In Eq. (2.28), the first term on the right-hand side is a dc quantity arising from second-order nonlinearity, the second is called the "fundamental," the third is the second harmonic, and the fourth is the third harmonic. We sometimes say that even-order nonlinearity introduces dc offsets.

From the above expansion, we make two observations. First, even-order harmonics result from  $\alpha_j$  with even j, and vanish if the system has odd symmetry, i.e., if it is fully differential. In reality, however, random mismatches corrupt the symmetry, yielding finite even-order harmonics. Second, in (2.28) the amplitudes of the second and third harmonics are proportional to  $A^2$  and  $A^3$ , respectively, i.e., we say the nth harmonic grows in proportion to  $A^n$ .

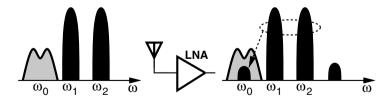

In many RF circuits, harmonic distortion is unimportant or an irrelevant indicator of the effect of nonlinearity. For example, an amplifier operating at 2.4 GHz produces a second harmonic at 4.8 GHz, which is greatly suppressed if the circuit has a narrow bandwidth. Nonetheless, harmonics must always be considered carefully before they are dismissed. The following examples illustrate this point.

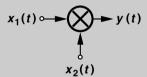

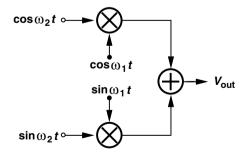

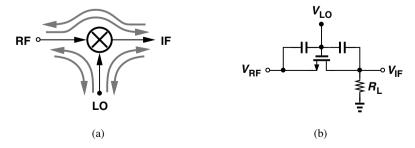

# Example 2.5

An analog multiplier "mixes" its two inputs as shown in Fig. 2.7, ideally producing  $y(t) = kx_1(t)x_2(t)$ , where k is a constant.<sup>3</sup> Assume  $x_1(t) = A_1 \cos \omega_1 t$  and  $x_2(t) = A_2 \cos \omega_2 t$ .

**Figure 2.7** *Analog multiplier.*

- (a) If the mixer is ideal, determine the output frequency components.

- (b) If the input port sensing  $x_2(t)$  suffers from third-order nonlinearity, determine the output frequency components.

#### **Solution:**

(a) We have

$$y(t) = k(A_1 \cos \omega_1 t)(A_2 \cos \omega_2 t) \tag{2.29}$$

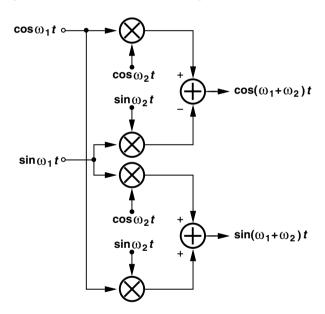

$$= \frac{kA_1A_2}{2}\cos(\omega_1 + \omega_2)t + \frac{kA_1A_2}{2}\cos(\omega_1 - \omega_2)t.$$

(2.30)

The output thus contains the sum and difference frequencies. These may be considered "desired" components.

(Continues)

<sup>3.</sup> The factor k is necessary to ensure a proper dimension for y(t).

# **Example 2.5** (Continued)

(b) Representing the third harmonic of  $x_2(t)$  by  $(\alpha_3 A_2^3/4) \cos 3\omega_2 t$ , we write

$$y(t) = k(A_1 \cos \omega_1 t) \left( A_2 \cos \omega_2 t + \frac{\alpha_3 A_2^3}{4} \cos 3\omega_2 t \right)$$

$$= \frac{kA_1 A_2}{2} \cos(\omega_1 + \omega_2) t + \frac{kA_1 A_2}{2} \cos(\omega_1 - \omega_2) t$$

$$+ \frac{k\alpha_3 A_1 A_2^3}{8} \cos(\omega_1 + 3\omega_2) t + \frac{k\alpha_3 A_1 A_2^3}{8} \cos(\omega_1 - 3\omega_2) t.$$

(2.31)

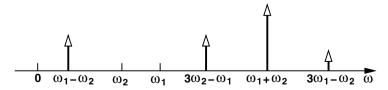

The mixer now produces two "spurious" components at  $\omega_1 + 3\omega_2$  and  $\omega_1 - 3\omega_2$ , one or both of which often prove problematic. For example, if  $\omega_1 = 2\pi \times (850 \text{ MHz})$  and  $\omega_2 = 2\pi \times (900 \text{ MHz})$ , then  $|\omega_1 - 3\omega_2| = 2\pi \times (1850 \text{ MHz})$ , an "undesired" component that is difficult to filter because it lies close to the desired component at  $\omega_1 + \omega_2 = 2\pi \times (1750 \text{ MHz})$ .

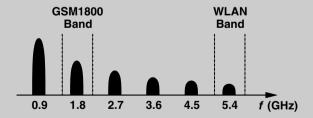

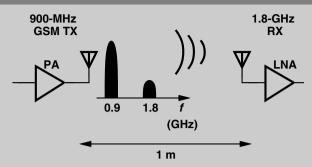

# Example 2.6

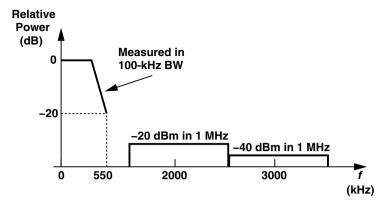

The transmitter in a 900-MHz GSM cellphone delivers 1 W of power to the antenna. Explain the effect of the harmonics of this signal.

#### **Solution:**

The second harmonic falls within another GSM cell phone band around 1800 MHz and must be sufficiently small to negligibly impact the other users in that band. The third, fourth, and fifth harmonics do not coincide with any popular bands but must still remain below a certain level imposed by regulatory organizations in each country. The sixth harmonic falls in the 5-GHz band used in wireless local area networks (WLANs), e.g., in laptops. Figure 2.8 summarizes these results.

Figure 2.8 Summary of harmonic components.

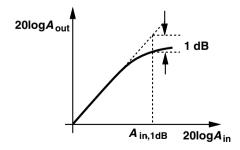

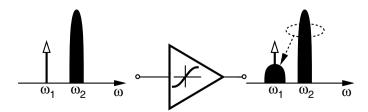

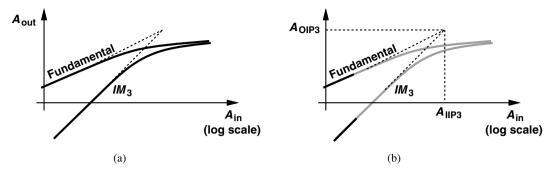

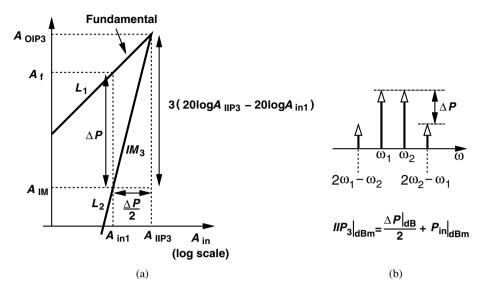

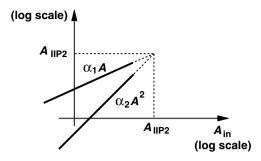

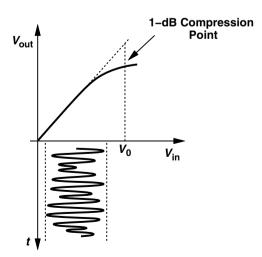

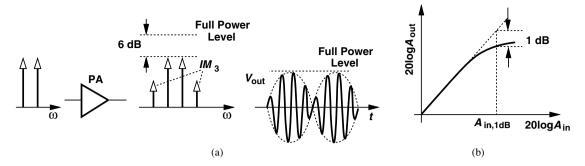

# 2.2.2 Gain Compression

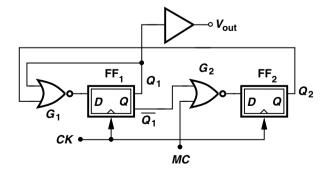

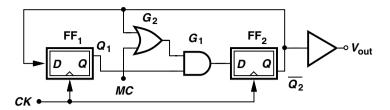

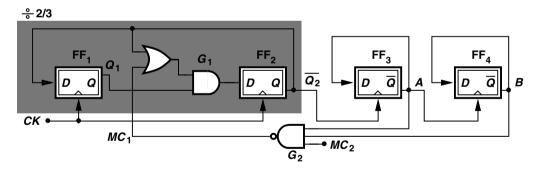

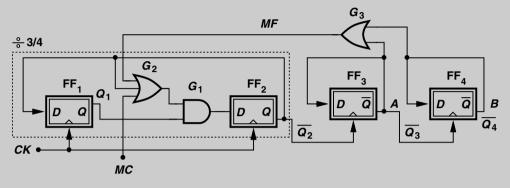

The small-signal gain of circuits is usually obtained with the assumption that harmonics are negligible. However, our formulation of harmonics, as expressed by Eq. (2.28), indicates