Physical Address Extension

In computing, Physical Address Extension (PAE), sometimes referred to as Page Address Extension,[1] is a memory management feature for the IA-32 architecture. PAE was first introduced in the Pentium Pro. It defines a page table hierarchy of three levels, with table entries of 64 bits each instead of 32, allowing these CPUs to access a physical address space larger than 4 gigabytes (232 bytes).

The page table structure used by x86-64 CPUs when operating in 64-bit mode further extends the page table hierarchy to four levels, extending the virtual address space, and uses additional physical address bits at all levels of the page table, extending the physical address space. It also uses the topmost bit of the 64-bit page table entry as an NX bit.

History

PAE was first implemented in the Intel Pentium Pro in 1995,[2] although the accompanying chipsets usually lacked support for the required extra address bits.[3]

PAE is supported by Intel Pentium Pro and later Pentium-series processors. The first Pentium M family processors ("Banias") also support PAE; however, they do not show the PAE support flag in their CPUID information.[4] It was also available on AMD processors including the AMD Athlon[5] (although the chipsets for are limited to 32-bit addressing[6]) and later AMD processor models.

When AMD defined their AMD64 architecture as an extension of x86, they defined an enhanced version of PAE[7] to be used while the processor was in 64-bit mode ("long mode"). It supports up to 48-bit virtual addresses,[8](p120) 52-bit physical addresses,[8](p24) and includes NX bit functionality. This version of PAE is the mandatory memory paging model in long mode on x86-64 processors; there is no "non-PAE mode" while in long mode.[9] The documentation for "Intel 64", the Intel version of x86-64, refers to these page table formats as "IA-32e paging" rather than "PAE".[10]

Design

With PAE, IA-32 architecture is augmented with additional address lines used to select the additional memory, so physical address size increases from 32 bits to 36 bits. This increases the physical memory addressable by the system from 4 GB to 64 GB. The 32-bit size of the virtual address is not changed, so regular application software continues to use instructions with 32-bit addresses and (in a flat memory model) is limited to 4 gigabytes of virtual address space. Operating systems supporting this mode use page tables to map the regular 4 GB address space into the physical memory, which, depending on the operating system, may be as big as 64 GB. The mapping is typically applied separately for each process, so that the extra memory is useful even though no single regular application can access it all simultaneously.

Later work associated with AMD's development of x86-64 architecture expanded the theoretical possible size of physical addresses to 52 bits.

Page table structures

In protected mode, x86 processors use a two-level page translation scheme, where the control register CR3 points to a single 4 KB long page directory divided into 1024 × 4 byte entries that point to 4 KB long page tables, similarly consisting of 1024 × 4 byte entries pointing to 4 KB long pages.

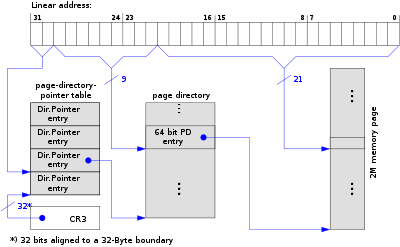

Enabling PAE (by setting bit 5, PAE, of the system register CR4) causes major changes to this scheme. By default, the size of each page remains as 4 KB. Each entry in the page table and page directory becomes 64 bit long (8 bytes), instead of 32 bits, to allow for additional address bits. However, the size of tables does not change, so both table and directory now have only 512 entries. Because this allows only one half of the entries of the original scheme, an extra level of hierarchy has been added, so CR3 now points to Page Directory Pointer Table, a short table containing four pointers to page directories.

The entries in the page directory have an additional flag in bit 7, named PS (for page size). If the system has set this bit to 1, the page directory entry does not point to a page table but to a single, large 2 MB page (Page Size Extension).

In all page table formats supported by x86 and x86-64, the 12 least significant bits of the page table entry are either interpreted by the memory management unit or are reserved for operating system use. In processors that implement the "no-execute" or "execution disable" feature, the most significant bit (bit 63) is the NX bit. The next eleven most significant bits (bits 52 through 62) are reserved for operating system use by both Intel and AMD's architecture specifications. Thus, from 64 bits in the page table entry, 12 low-order and 12 high-order bits have other uses, leaving 40 bits (bits 12 though 51) for the physical page number. Combined with 12 bits of "offset within page" from the linear address, a maximum of 52 bits are available to address physical memory. This allows a maximum RAM configuration of 252 bytes, or 4 petabytes (about 4.5×1015 bytes).

On x86-64 processors in native long mode, the address translation scheme uses PAE but adds a fourth table, the 512-entry page-map level 4 table, and extends the page directory pointer table to 512 entries instead of the original 4 entries it has in protected mode. Currently 48 bits of virtual page number are translated, giving a virtual address space of up to 256 TB.[8](p120) In the page table entries, in the original specification, 40 bits of physical page number are implemented.

- Page table structures

-

No PAE, 4 KB pages

-

No PAE, 4 MB pages

-

With PAE; 4 KB pages

-

With PAE; 2 MB pages

Support

Software can identify via the CPUID flag PAE whether a CPU supports PAE mode or not. A free-of-charge program for Microsoft Windows is available which will list many processor capabilities, including PAE support.[11] In Linux, commands such as cat /proc/cpuinfo can list the pae flag when present,[12] as well as other tools such as the SYSLINUX Hardware Detection Tool.

To use PAE, motherboard and operating system support is required.

Operating system support

Microsoft Windows

Microsoft Windows supports PAE if booted with the appropriate option, but according to Geoff Chappell, Microsoft may limit 32-bit versions of Windows to 4 GB as a matter of its licensing policy.[13] Microsoft Technical Fellow Mark Russinovich says that some drivers were found to be unstable when encountering physical addresses above 4 GB.[14]

The following table shows the memory limits for 32-bit versions of Microsoft Windows:

| Windows Version | Memory limit |

|---|---|

| Windows 2000 Professional, Server | 4 GB |

| Windows 2000 Advanced Server | 8 GB |

| Windows 2000 Datacenter | 32 GB |

| Windows XP Starter | 0.5 GB |

| Windows XP (Other editions) | 4 GB |

| Windows Server 2003 Web SP2 | 2 GB |

| Windows Server 2003 Standard SP2 | 4 GB |

| Windows Server 2003 Enterprise/Datacenter SP2 | 64 GB |

| Windows Storage Server 2003 Enterprise | 8 GB |

| Windows Storage Server 2003 (other editions) | 4 GB |

| Windows Home Server | 4 GB |

| Windows Vista Starter | 1 GB |

| Windows Vista (Other editions) | 4 GB |

| Windows Server 2008 Standard, Web | 4 GB |

| Windows Server 2008 Enterprise, Datacenter | 64 GB |

| Windows 7 Starter | 2 GB |

| Windows 7 (Other editions) | 4 GB |

| Windows 8 (all editions) | 4 GB |

| Windows 10 (all editions) | 4 GB |

The original releases of Windows XP and Windows XP SP1 used PAE mode to allow RAM to extend beyond the 4 GB address limit. However, it led to compatibility problems with 3rd party drivers which led Microsoft to remove this capability in Windows XP Service Pack 2. Windows XP SP2 and later, by default, on processors with the no-execute (NX) or execute-disable (XD) feature, runs in PAE mode in order to allow NX.[18] The no execute (NX, or XD for execution disable) bit resides in bit 63 of the page table entry and, without PAE, page table entries on 32-bit systems have only 32 bits; therefore PAE mode is required in order to exploit the NX feature. However, "client" versions of 32-bit Windows (Windows XP SP2 and later, Windows Vista, Windows 7) limit physical address space to the first 4 GB for driver compatibility [14] via the licensing limitation mechanism,[13] even though these versions do run in PAE mode if NX support is enabled.

Windows 8 will only run on processors which support PAE, in addition to NX and SSE2.[19]

OS X

Mac OS X Tiger through Mac OS X Snow Leopard support PAE and the NX bit on IA-32 processors; Snow Leopard was the last version to support IA-32 processors. All Intel versions of OS X use 4-level paging (IA-32e paging rather than PAE) to address memory above 4GB for Intel 64 processors. Mac Pro and Xserve systems can use up to 64 GB of RAM.[20]

Linux

The Linux kernel includes full PAE mode support starting with version 2.3.23,[21] enabling access of up to 64 GB of memory on 32-bit machines. A PAE-enabled Linux kernel requires that the CPU also support PAE. The Linux kernel supports PAE as a build option and major distributions provide a PAE kernel either as the default or as an option.

The NX bit feature requires a kernel built with PAE support.[22]

Linux distributions now commonly use a PAE-enabled kernel as the default, a trend that began in 2009.[23] As of 2012 many, including Red Hat Enterprise Linux / CentOS, Ubuntu (and derivatives like Xubuntu and Linux Mint),[24][25][26] have stopped distributing non-PAE kernels, thus making PAE hardware mandatory. Linux distributions which require PAE may refuse to boot on Pentium M family processors because they do not show the PAE support flag in their CPUID information (even though it is supported internally).[4]

Distributions that still provide a non-PAE option, including Debian (and derivatives like LMDE 2 (Linux Mint Debian Edition)[27]), Slackware, and LXLE typically do so with "i386", "i486" or "retro" labels.[28][29]

Others

FreeBSD and NetBSD also support PAE as a kernel build option. FreeBSD supports PAE in the 4.x series starting with 4.9, in the 5.x series starting with 5.1, and in all 6.x and later releases. Support requires the kernel PAE configuration-option. Loadable kernel modules can only be loaded into a kernel with PAE enabled if the modules were built with PAE enabled; the binary modules in FreeBSD distributions are not built with PAE enabled, and thus cannot be loaded into PAE kernels. Not all drivers support more than 4 GB of physical memory; those drivers won't work correctly on a system with PAE.[30]

OpenBSD has had support for PAE since 2006 with the standard GENERIC i386 kernel. GeNUA mbH supported the initial implementation.[31] Since release 5.0 PAE has had a series of changes, in particular changes to i386 MMU processing for PMAP, see pmap(9).[32]

Solaris supports PAE beginning with Solaris version 7. However, third-party drivers used with version 7 which do not specifically include PAE support may operate erratically or fail outright on a system with PAE.[33]

Haiku added initial support for PAE sometime after the R1 Alpha 2 release. With the release of R1 Alpha 3 PAE is now officially supported.

See also

- Page Size Extension

- PCI hole

- PSE-36

- Architecture of Windows NT

- 3 GB barrier

- Large Physical Address Extension (LPAE) – in the ARM architecture

References

- ↑ Dual-Core Intel® Xeon® Processor 2.80 GHz Specification Update (PDF). Intel Corporation. October 2006. p. 18.

- ↑ T. Shanley (1998). Pentium Pro and Pentium II System Architecture. Addison-Wesley Professional. p. 439. ISBN 978-0-201-30973-7.

- ↑ "Operating Systems and PAE Support". Hardware Developers Center. 14 July 2006. Retrieved 20 April 2014.

- 1 2 PAE - Ubuntu Community Help Wiki

- ↑ "AMD Athlon 500 - AMD-K7500MTR51B C". Cpu-world.com. 26 March 2014. Retrieved 20 April 2014.

- ↑ AMD-762 System Controller (p. 2): "Supports up to 4 Gbytes of memory"

- ↑ AMD Corporation (September 2012). "Volume 2: System Programming" (PDF). AMD64 Architecture Programmer's Manual. AMD Corporation. Retrieved 2015-02-07.

Long-mode page translation requires the use of physical-address extensions (PAE).

- 1 2 3 AMD Corporation (September 2012). "Volume 2: System Programming" (PDF). AMD64 Architecture Programmer's Manual. AMD Corporation. Retrieved 2015-02-07.

- ↑ "Volume 2: System Programming" (PDF). AMD64 Architecture Programmer's Manual. Advanced Micro Devices. November 1, 2009. pp. 124–143. Retrieved 2015-02-07.

Long-mode page translation requires the use of physical-address extensions (PAE). Before activating long mode, PAE must be enabled by setting

CR4.PAEto1. Activating long mode before enabling PAE causes a general-protection exception (#GP) to occur. - ↑ "Volume 3A: System Programming Guide, Part 1" (PDF). Intel® 64 and IA-32 Architectures Software Developer’s Manual. Intel Corporation. January 2015. pp. 4–19 through 4–29. Retrieved 2015-02-07.

A logical processor uses IA-32e paging if CR0.PG = 1, CR4.PAE = 1, and IA32_EFER.LME = 1.

- ↑ "Microsoft Sysinternals: Coreinfo". Windows Sysinternals. Microsoft. 19 December 2013. Retrieved 20 April 2014.

- ↑ "Detecting your Hardware". Gentoo. October 8, 2008. Retrieved 2013-04-28.

- 1 2 Chappell, Geoff. "Licensed Memory in 32-Bit Windows Vista". geoffchappell.com. WP:SPS. Retrieved 20 April 2014.

- 1 2 Mark Russinovich (2008-07-21). "Pushing the Limits of Windows: Physical Memory". Retrieved 2010-07-11.

- ↑ "Memory Limits for Windows releases". MSDN. Microsoft. December 5, 2007. Retrieved 2015-11-16.

- ↑ "Intel Physical Addressing Extensions (PAE) in Windows 2000". Support. Microsoft. October 26, 2007. Retrieved 2007-12-29.

- ↑ "Overview of Windows Server 2003 R2 Datacenter Edition". TechNet. Microsoft. Retrieved 2009-05-15.

- ↑ "The RAM reported by the System Properties dialog box and the System Information tool is less than you expect in Windows Vista or in Windows XP Service Pack 2 or later version (MSKB 888137)". Knowledge Base. Microsoft. Retrieved 2009-01-30.

- ↑ Khurshid, Usman (2 November 2012). "How To Check If Your Processor Supports PAE, NX And SSE2 For Windows 8 Installation". technize.net. Technize. Retrieved 20 April 2014.

- ↑ "Road to Mac OS X 10.6 Snow Leopard: 64-Bits". 2008-09-26. Retrieved 2008-09-26.

- ↑ "2.3.23-pre4 x86 64 GB RAM changes [HIGHMEM patch] explained a bit".

- ↑ Professional Linux Kernel Architecture, Figure 3.16 Code flow for paging_init, "Execute Disable Protection is also enabled if supported by processor and if the kernel was compiled with PAE support; unfortunately, the feature is otherwise not available."

- ↑ "x86 Specifics for Fedora 11".

- ↑ "Xubuntu 12.04 released". Xubuntu.org. April 26, 2012. Retrieved 24 October 2015.

The non-PAE kernel will not be available in future Xubuntu releases.

- ↑ "EnablingPAE". Retrieved 2013-04-28.

- ↑ "RHEL 6 Release Notes, 12.6. General Kernel Updates 12.6.1. Physical Address Extension (PAE)". RedHat. Retrieved 27 November 2013.

- ↑ "Known problems in Linux Mint Debian".

To guarantee compatibility with non-PAE processors, the 32-bit versions of Linux Mint Debian come with a 486 kernel by default.

- ↑ "Precise Puppy". puppylinux.org. PuppyLinux. Retrieved 20 April 2014.

- ↑ "2.1. Supported Hardware". Debian GNU/Linux Installation Guide. SPI. Retrieved 20 April 2014.

- ↑ "FreeBSD PAE(4) man page". 2003-04-08. Retrieved 2007-11-26.

- ↑ "PAE for OpenBSD/i386 by Michael Shalayeff, NYC". 2006. Retrieved 2014-09-03.

- ↑ "OpenBSD pmap(9) man page". Retrieved 2014-09-03.

- ↑ "Solaris 7 5/99 Release Notes (Intel Platform Edition), Appendix B: Hardware Compatibility List and Device Configuration Guide (Intel Platform Edition) 5/99". 1999. Retrieved 2007-11-26.

Further reading

- "Intel 64 and IA-32 Architectures Software Developer's Manual, Volume 3A: System Programming Guide, Part 1". Intel. 11 February 2014.

- "Physical Address Extension". MSDN. Microsoft.