Cray X-MP

| |

|

The CERN CRAY-XMP48 displayed at the EPFL in Switzerland. | |

| Manufacturer | Cray Research |

|---|---|

| Type | Supercomputer |

| Release date | 1982 |

| Predecessor | Cray-1 |

The Cray X-MP is a supercomputer designed, built and sold by Cray Research. It was announced in 1982 as the "cleaned up" successor to the 1975 Cray-1, and was the world's fastest computer from 1983 to 1985.[1] The principal designer was Steve Chen.

Description

The X-MP's main improvement over the Cray-1 was that it was a shared-memory parallel vector processor, the first such computer from Cray Research. It housed two CPUs in a mainframe that was nearly identical in outside appearance to the Cray-1.

The X-MP CPU had a faster 9.5 nanosecond clock cycle (105 MHz), compared to 12.5 ns for the Cray-1A. It was built from bipolar gate-array integrated circuits containing 16 emitter-coupled logic gates each. The CPU was very similar to the Cray-1 CPU in architecture, but had better memory bandwidth (with two read ports and one write port to the main memory instead of only one read/write port) and improved chaining support. Each CPU had a theoretical peak performance of 200 MFLOPS, for a peak system performance of 400 MFLOPS.[2]

The X-MP initially supported 2 million 64-bit words (16 MB) of main memory in 16 banks, respectively. Memory bandwidth was significantly improved over the Cray-1—instead of one port for both reads and writes, there were now two read ports, one write port, and one dedicated to I/O. The main memory was built from 4 Kbit bipolar SRAM ICs. CMOS memory versions of the Cray-1M were renamed Cray X-MP/1s. This configuration was first used for Cray Research's UNIX port.

In 1984, improved models of the X-MP were announced, consisting of one, two, and four-processor systems with 4 and 8 million word configurations. The top-end system was the X-MP/48, which contained four CPUs with a theoretical peak system performance of over 800 MFLOPS and 8 million words of memory.[2] The CPUs in these models introduced vector gather/scatter memory reference instructions to the product line. The amount of main memory supported was increased to a maximum of 16 million words, depending on the model. The main memory was built from bipolar or MOS SRAM ICs, depending on the model.

The system initially ran the proprietary Cray Operating System (COS) and was object-code compatible with the Cray-1. A UNIX System V derivative initially named CX-OS and finally renamed UniCOS ran through a guest operating system facility. UniCOS became the main OS from 1986 onwards. The DOE ran the Cray Time Sharing System OS instead. See the Software section for the Cray 1 for a more detailed elaboration of software (language compiler, assembler, OSes, and applications) as X-MPs and 1s were mostly compatible.

Extended Architecture series

Cray Research announced the X-MP Extended Architecture series in 1986. The EA series CPU had an 8.5 ns clock cycle (117 MHz), and was built from macrocell array and gate array ICs. The EA series extended the width of the A and B registers to 32 bits and performed 32-bit address arithmetic, increasing the amount of memory theoretically addressable to 2 billion words. The largest configuration produced was 64 million words of MOS SRAM in 64 banks. For compatibility with existing software written for the Cray-1 and older X-MP models, 24-bit addressing was also supported. Each EA series CPU's peak performance was 234 MFLOPS. For a four-processor system, the peak performance was 942 MFLOPS.

I/O subsystem

The Input/Output (I/O) subsystem could have two to four I/O processors with a total of 2 to 32 disk storage units. The DD-39 and DD-49 hard drives made by Ibis with a raw transfer rate of 13.3 MB/s each stored 1200 megabyte (blocked and formatted) with 5.9 MB/s and 9.8 MB/s transfer rates (unstriped), respectively. Optional solid state drives were available with 256, 512 or 1024 MB capacities with transfer rates of 100 to 1,000 MB/s per channel. Up to 38 gigabytes of data storage was possible.[2][3]

For magnetic tape I/O, the system could interface with IBM 3420 and 3480 tape units directly without a lot of CPU processing.[3]

Pricing

A 1984 X-MP/48 cost about US$15 million plus the cost of disks. In 1985 Bell Labs purchased a Cray X-MP/24 for $10.5 million along with eight DD-49 1.2 GB drives for an additional $1 million. They received $1.5 million of trade-in credit for their Cray-1.[4]

Successors

The Cray-2, a completely new design, was introduced 1985. A very different compact four-processor design with from 64 MW (megaword) to 512 MW (512 MB to 4 GB) of main memory, it was specified to 500 MFLOPS but was slower than the X-MP on certain calculations due to its high memory latency.

The X-MP-succeeding Cray Y-MP series was announced in 1988; it also had a new design, replacing the 16-gate ECL gate arrays with a more compact VLSI gate array with larger circuit boards. It was a major improvement of the X-MP supporting up to eight processors.

Usage

- The short film "The Adventures of André and Wally B.", released in 1984 by The Graphics Group, a then-Lucasfilm subsidiary which would later become Pixar, used an X-MP/48 for much of its rendering. Special thanks is given to Cray Research in the short's credits for use of the machine.

- The 1984 film The Last Starfighter depended heavily on high polygon count (for the time) models with complex lighting effects, the rendering of which was made possible by the use of the X-MP.[5]

Image gallery

-

Control panel of the CRAY X-MP/48

-

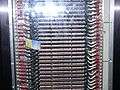

Logic boards of the CRAY X-MP/48

-

Power system of the CRAY X-MP/48

-

CRAY X-MP/24 at Barcelona Supercomputing Center

-

CRAY X-MP/24 at Barcelona Supercomputing Center

References

- ↑ Steinhauser, Martin Oliver (2008). Computational Multiscale Modeling of Fluids and Solids: Theory and Applications. Springer. p. 21. ISBN 9783540751168.

- 1 2 3 Cray Research, Inc. (1985). "The Cray X-MP Series of Computer Systems".

- 1 2 Cray Research, Inc. (1986). "The Cray X-MP Series of Computer Systems".

- ↑ Dennis Ritchie (September 2000). "Two Cray X/MP papers". Retrieved 2009-04-02.

- ↑ Ohio State University CG history page

Further reading

- Keith Robbins and S. Robbins (1989) Lecture Notes in Computer Science: The Cray X-MP/Model 24 Springer ISBN 3-540-97089-4

External links

Media related to Cray-XMP48 at Wikimedia Commons

Media related to Cray-XMP48 at Wikimedia Commons

| Records | ||

|---|---|---|

| Preceded by Cray-1 136 megaflops |

World's most powerful supercomputer 1983–1985 |

Succeeded by Cray-2 1.95 gigaflops (peak) |